C141-E090-01EN5 - 2

5.1 Physical Interface

5.1.1 Interface signals

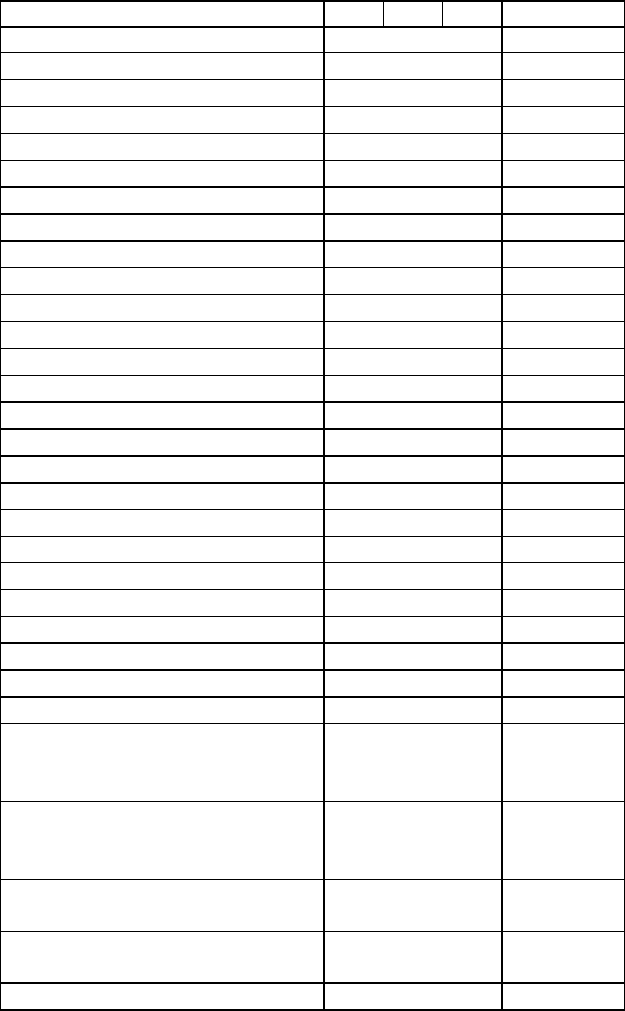

Table 5.1 shows the interface signals.

Table 5.1 Interface signals

Description Host Dir Dev Acrorym

Cable select see note CSEL

Chip select 0

→

CS0–

Chip select 1

→

CS1–

Data bus bit 0

↔

DD0

Data bus bit 1

↔

DD1

Data bus bit 2

↔

DD2

Data bus bit 3

↔

DD3

Data bus bit 4

↔

DD4

Data bus bit 5

↔

DD5

Data bus bit 6

↔

DD6

Data bus bit 7

↔

DD7

Data bus bit 8

↔

DD8

Data bus bit 9

↔

DD9

Data bus bit 10

↔

DD10

Data bus bit 11

↔

DD11

Data bus bit 12

↔

DD12

Data bus bit 13

↔

DD13

Data bus bit 14

↔

DD14

Data bus bit 15

↔

DD15

Device active or slave present see note DASP–

Device address bit 0

→

DA0

Device address bit 1

→

DA1

Device address bit 2

→

DA2

DMA acknowledge

→

DMACK–

DMA request

←

DMARQ

Interrupt request

←

INTRQ

I/O read

→

DIOR–

DMA ready during Ultra DMA data in bursts

→

HDMARDY–

Data strobe during Ultra DMA data out bursts

→

HSTROBE

I/O ready

←

IORDY

DMA ready during Ultra DMA data out bursts

←

DDMARDY–

Data strobe during Ultra DMA data in bursts

←

DSTROBE

I/O write

→

DIOW–

Stop during Ultra DMA data bursts

→

STOP

Passed diagnostics see note PDIAG–

Cable type detection CBLID–

Reset

→

RESET–

Note See signal descriptions