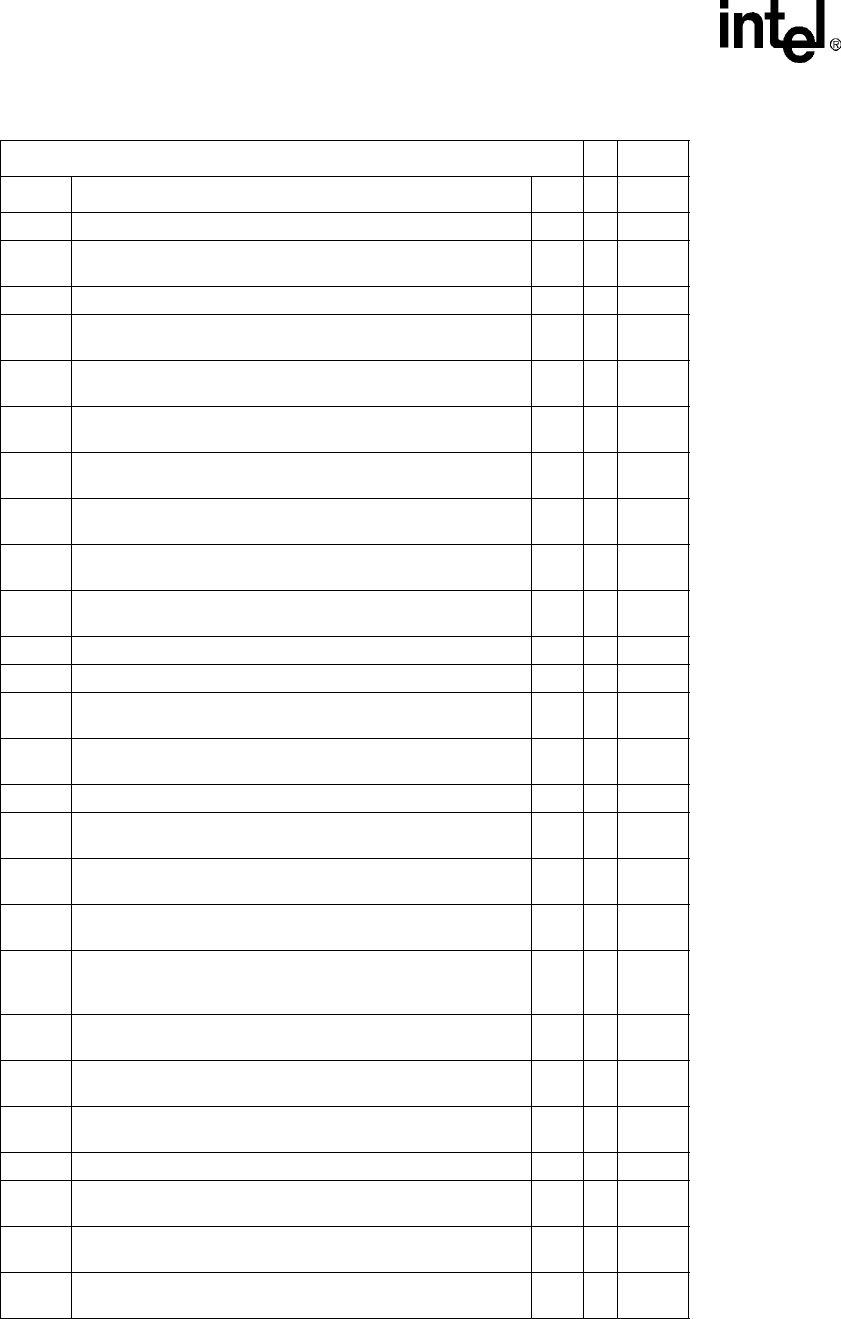

10 Intel® PXA27x Processor Family Specification Update

Summary of Changes

11 KBD: Extra Keypad matrix interrupt in IMKP Mode 16 X No Fix

12

USBH: USBH Register UHCRHPSx[CCS] Bit Set Incorrectly

After Power On

17 X No Fix

13 AC97: Command Done bit remains set after an AC97 cold reset 17 X No Fix

14

POWER MANAGER: Fast Ramp rates on voltage pins can

cause high current consumption.

17 X No Fix

15

LCD: Reconfiguring the LCD controller retains the previous PPL

value for the first line.

18 X No Fix

16

MSHC: Memory Stick does not come out of SLEEP mode after

wake up process.

19 X No Fix

17

LCD: Overlay1 is not enabled intermittently after re-enabling

LCD.

19 X Plan Fix

18

POWER MANAGER: Processor ignores BATT/VCC faults while

exiting sleep mode.

20 X No Fix

19

KBD: Keyboard Edge-Detect Status Register Incorrect After

Standby Mode Wakeup.

20 X No Fix

20

UART: Character Timeout interrupt remains set under certain

software conditions

21 X No Fix

21 LCD: LCD not enabling in dual panel mode. 21 X No Fix

22 UDC: UDC does not correctly support alternate interfaces. 22 X No Fix

23

ICP: Receiver Aborts randomly occur prematurely and without

End of frame/Error in FIFO interrupt

23 X No Fix

24

SSP: OSTimer counter increments incorrectly for SSP Frames

in Network mode

23 X No Fix

25 LCD: Enabling Overlay 2 for YUV420 hangs LCD controller. 23 X Plan Fix

26

USBOTG: Unable to measure duration of Single-Ended Zero

(SE0) for Session Request Protocol (SRP)

24 X Plan Fix

27

MEMC: Write/Read to/from SDRAM can collide with alternate

bus master mode when MDREFR:ALTREFB is set.

25 X No Fix

28

Power Manger: Core hangs during voltage change when there

are outstanding transactions on the bus

25 X No Fix

29

MMC: MMC unit in SPI mode always waits a minimum of 1 Ncx

cycles, even though the MMC spec dictates that SPI mode

CMD9 can have a minimum of 0 Ncx cycles.

27 X Plan Fix

30

SD: SD Controller in SPI mode not receiving data response for

CMD9 and CMD10 from some SD Cards

27 X Plan Fix

31

MEMC: SDRAM Refresh Commands are issued too often

during a VLIO access while BREQ is asserted.

28 X No Fix

32

Interrupt Controller: Unexpected exception vector when

ICCR[DIM]=0 and ICMR=0.

28 X No Fix

33 SSP: TXD line does not tristate when SSP is Slave to Frame 29 X No Fix

34

PowerManager: Simultaneous BATT and VDD faults results in

going to DeepSleep mode twice.

29 X No Fix

35

CORE: Non-branch instruction in vector table may execute

twice after a thumb mode exception

29 X No Fix

36

UART: UART does not correctly indicate a Framing Error

Interrupt in DMA mode.

30 X No Fix

Table 3. Summary of Errata (Sheet 2 of 3)

References C0 Status

Number Title Page