Intel® PXA27x Processor Family Specification Update 9

Summary of Changes

Summary of Changes

The following tables summarize the errata, specification changes, specification clarifications, and

documentation changes that apply to the Intel® PXA27x Processor Family.

Intel might fix some of

the errata in a future stepping of the component and account for the other outstanding issues

through documentation or specification changes as noted.

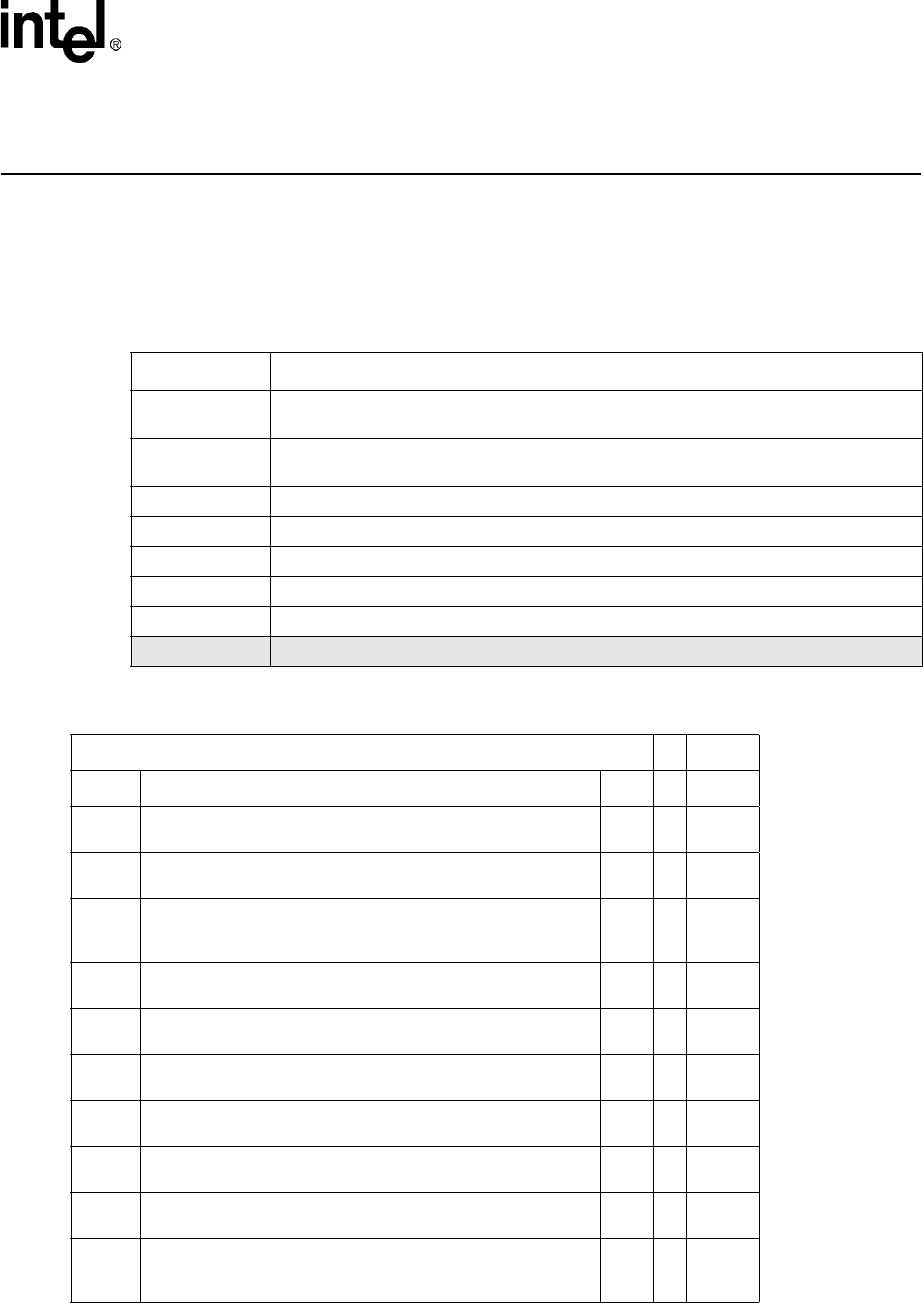

These tables use the following notations:

Notation Meaning

X

This erratum exists in the stepping indicated. specification change or clarification that

applies to this stepping.

(No mark) or

(Blank Box)

This erratum is fixed in the listed stepping, or the specification change does not apply to the

listed stepping.

Plan Fix This erratum might be fixed in a future stepping of the product.

Fixed This erratum has been previously fixed.

No Fix There are no plans to fix this erratum.

Doc Intel plans to update the appropriate documentation in a future revision.

No Bug This erratum has been determined to be a false erratum.

Shaded This item is either new or modified from the previous version of the document.

Table 3. Summary of Errata (Sheet 1 of 3)

References C0 Status

Number Title Page

1

CORE: IFU misses an external abort when a lock command is

outstanding

13 X No Fix

2

CORE: Aborted store that hits D-cache might mark write-back

data as dirty

13 X No Fix

3

CORE: Performance Monitor Unit Counts, using performance

monitoring event number 0x1, can be incremented erroneously

by unrelated core events

14 X No Fix

4

CORE: In SDS mode, back-to-back memory operations where

the first instruction aborts might hang

14 X No Fix

5

CORE: Lock aborts resulting from I-cache or I-TLB lock

operations are not presented properly on the trace interface

14 X No Fix

6

CORE: CP15 ID register accesses with opcode2 > 0b001 return

unpredictable values

15 X No Fix

7

CORE: Disabling and re-enabling the MMU can hang the core

or cause it to execute the wrong code

15 X No Fix

8

CORE: JTAG parallel register updates require an extra TCK

rising edge

16 X No Fix

9

MMC: SPI mode – if card is deselected, PROG_DONE will not

be set

16 X No Fix

10

MEMC: No MRS command is given when exiting from Alternate

Bus Master Mode when SA1111 Address Muxing Mode is

enabled

16 X No Fix