36 Intel® PXA27x Processor Family Specification Update

Errata

Implication: TBD

Workaround: To disable a PWMx clock, CKEN[1:0] must be 0b00.

Status: No Fix

E48. ICP: Occasionally EIF, EOF and CRC interrupt are missed when a

CRC error is received.

Problem: On some of the product points, occasionally the EIF, EOF, and CRC interrupts are missed when a

CRC error is received.

If you read the data out of the RX FIFO, the last piece of data does set the EOF and CRC status

bits, but the EIF bit never gets set.

If the interrupt latency is increased by approximately 20usec, the correct behavior is seen. Interrupt

latency equals the time from when the ICP generates the interrupt to the time the processor is able

to service the interrupt. Latency can be increased by looping on the OS timer until 20us has past.

Implication: If the ICP received a CRC error and is configured to use interrupts, occasionally the EIF, EOF, and

CRC interrupts are missed when a CRC error is received.

Workaround: Configure the ICP to use DMA-mode for data transfers. Do not attempt to use interrupt-mode for

data transfers.

Status: No Fix

E49. POWER MANAGER: Batt Fault does not always re-enable GPIO 0 and

GPIO 1 as wake-up sources.

Problem:

If the 13MHz oscillator is disabled during sleep mode, the processor does not comply to the

following statement in section 3.8.1.4 of the Intel® PXA27x Processor Family Developer’s

Manual:

“When nVDD_FAULT or nBATT_FAULT is asserted, PWER assumes its reset value,

enabling only GPIO<1:0> as wake-up sources.”

If the following sequence is performed:

1. The PWER[1:0] bits are cleared, which disables wake-up due to GPIO<1:0> edge detect

2. The PCFR[OPDE] bit is set, which disables the 13MHz oscillator during sleep mode

3. The processor is put into sleep mode

4. A nVDD_FAULT or nBATT_FAULT is asserted

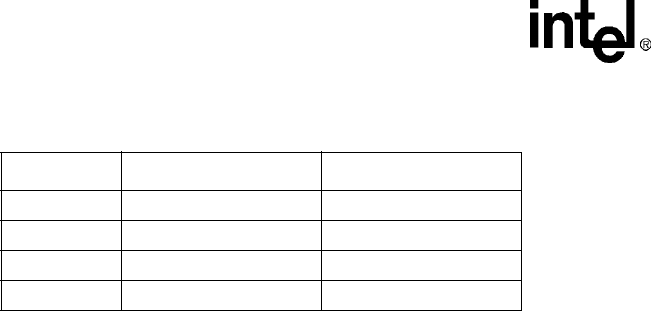

CKEN[1:0] Current Spec New Spec

0b00 All PWMs disabled All PWMs disabled

0b01 PWM0, PWM2 enabled All PWMs enabled

0b10 PWM1, PWM3 enabled All PWMs enabled

0b11 All PWMs enabled All PWMs enabled