Processor and Chipset Intel® Server Board SDS2

Revision 1.2

Order Number: A85874-002

8

3.2.2 I

2

C Bus

An I

2

C* bus is between the BMC and the six DIMM slots. This bus is used by the system BIOS to

retrieve DIMM information needed to program the HE-SL memory registers which are required to

boot the system.

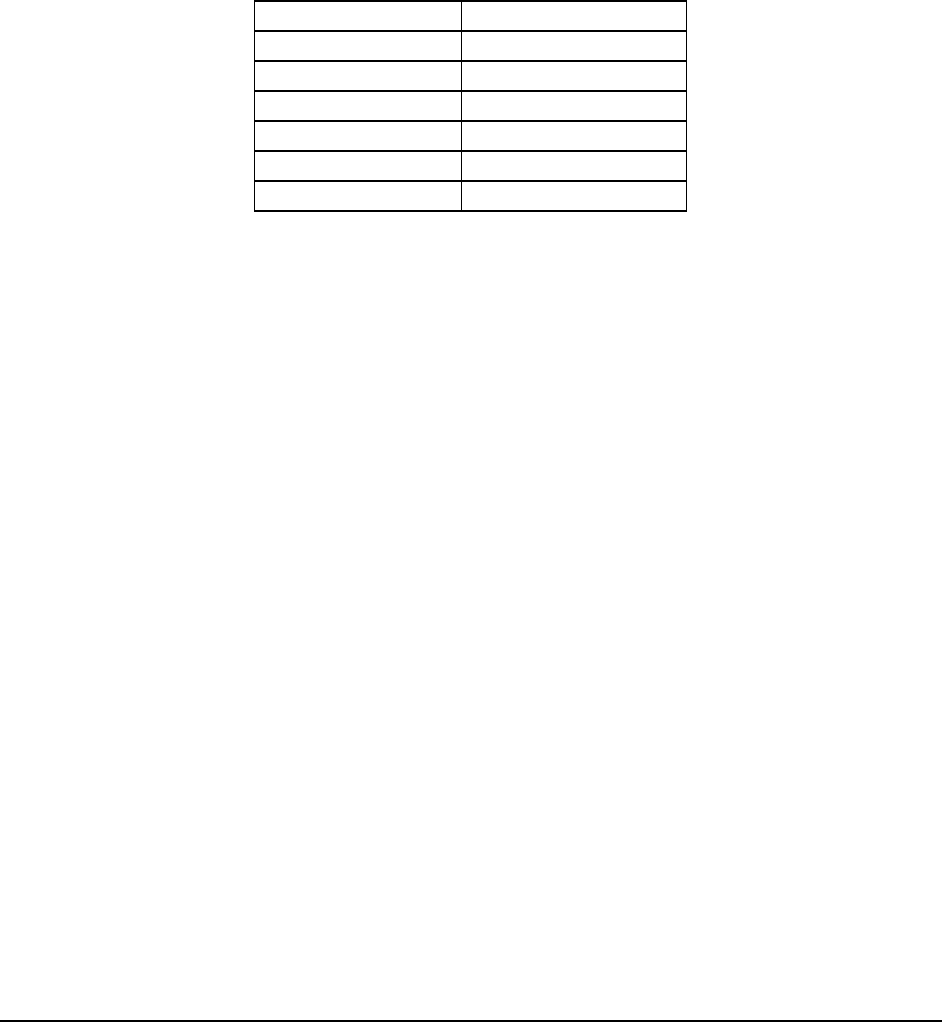

The following table provides the I

2

C addresses for each DIMM slot.

Table 3. I

2

C Addresses for DIMM Slots

Device Address

DIMM 1A 0xA0

DIMM 1B 0xA2

DIMM 2A 0xA4

DIMM 2B 0xA6

DIMM 3A 0xA8

DIMM 3B 0xAA

3.3 Chipset

The Server Works* ServerSet III HE-SL chipset provides an integrated I/O bridge and memory

controller and a flexible I/O subsystem core (PCI), targeted for multiprocessor systems and

standard high-volume servers. The Server Works* ServerSet III chipset consists of the three

components listed below:

• CNB20HE-SL: Champion North Bridge. The HE-SL North Bridge is responsible for

accepting access requests from the host (processor) bus and for directing those

accesses to memory or to one of the PCI buses. The HE-SL monitors the host bus,

examining addresses for each request. Accesses may be directed to a memory request

queue, for subsequent forwarding to the memory subsystem, or to an outbound request

queue, for subsequent forwarding to one of the PCI buses. The HE-SL also accepts

inbound requests from the CIOB20 and the legacy PCI bus. The HE-SL is also

responsible for generating the appropriate controls to control data transfer to and from

the memory.

• CIOB20: Champion I/O Bridge. The CIOB20 provides the interface for two 64-bit, 66-

MHz Rev. 2.2 compliant PCI bus. The CIOB is both master and target on both PCI

buses.

• CSB5: South Bridge. The CSB5 controller has several components. It provides the

interface for a 32-bit, 33-MHz Rev. 2.2-compliant PCI bus. The CSB5 can be both a

master and a target on that PCI bus. The CSB5 also includes a USB controller and an

IDE controller. The CSB5 is also responsible for much of the power management

functions, with ACPI control registers built in. The CSB5 also provides a number of GPIO

pins and has the LPC bus to support low-speed legacy I/O.