Server Management Intel® Server Board SDS2

Revision 1.2

Order Number: A85874-002

32

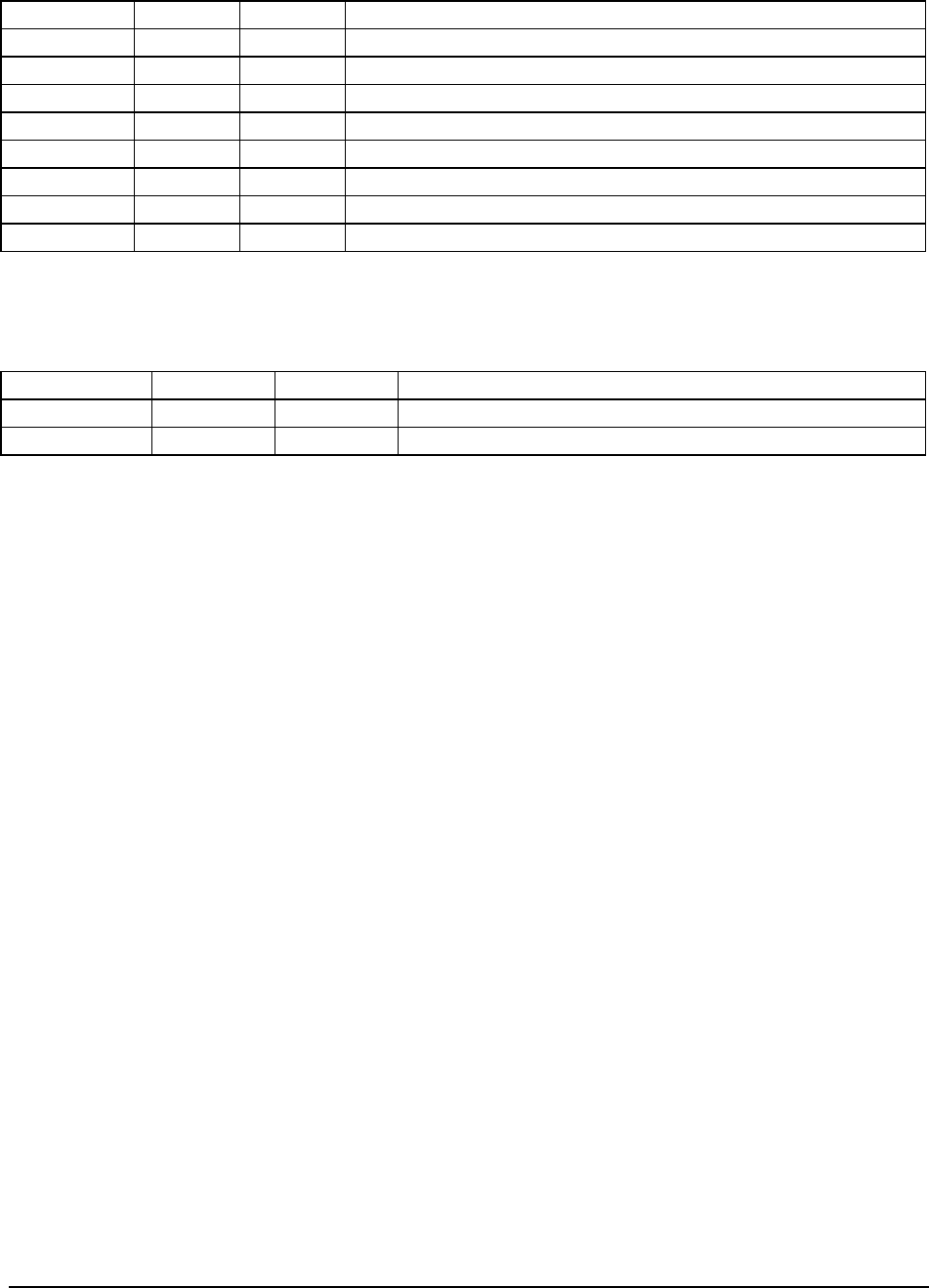

Function Voltage Address Notes

CSB5 3.3 V 0xC2 South Bridge

DIMM 1 3.3 V 0xA0

DIMM 2 3.3 V 0xA2

DIMM 3 3.3 V 0xA4

DIMM 4 3.3 V 0xA6

DIMM 5 3.3 V 0xA8

DIMM 6 3.3 V 0xAA

PCK2001M 3.3 V 0xD2 Clock Buffers

Table 21. Private I

2

C Bus 4 Devices

Function Voltage Address Notes

NIC1 3 VSB 0x84

NIC2 3VSB 0x86

5.4 Error Reporting

This section documents the types of system bus error conditions monitored by the SDS2 Server

Board.

5.4.1 Error Sources and Types

One of the major requirements of server management is to correctly and consistently handles

system errors. System errors on the SDS2, which can be disabled and enabled individually, can

be categorized as follows:

• PCI bus

• Processor bus errors

• Memory single- and multi-bit errors

• General server management sensors, managed by the Sahalee BMC

5.4.2 PCI Bus Errors

The PCI bus defines two error pins, PERR# and SERR#, for reporting PCI parity errors and

system errors, respectively. In the case of PERR#, the PCI bus master has the option to retry

the offending transaction, or to report it using SERR#. All other PCI-related errors are reported by

SERR#. SERR# is routed to NMI if enabled by BIOS.

5.4.3 Intel® Pentium® III Processor Bus Errors

The HE-SL supports all the data integrity features supported by the Pentium Pro bus including

Address, Request and Response parity. The HE-SL always generates ECC data while it is driving

the processor data bus although data bus ECC can be disabled or enabled by BIOS (enabled by

default). The HE-SL generates MIRQ# on SBEs (Single-bit errors) and generates SALERT# on