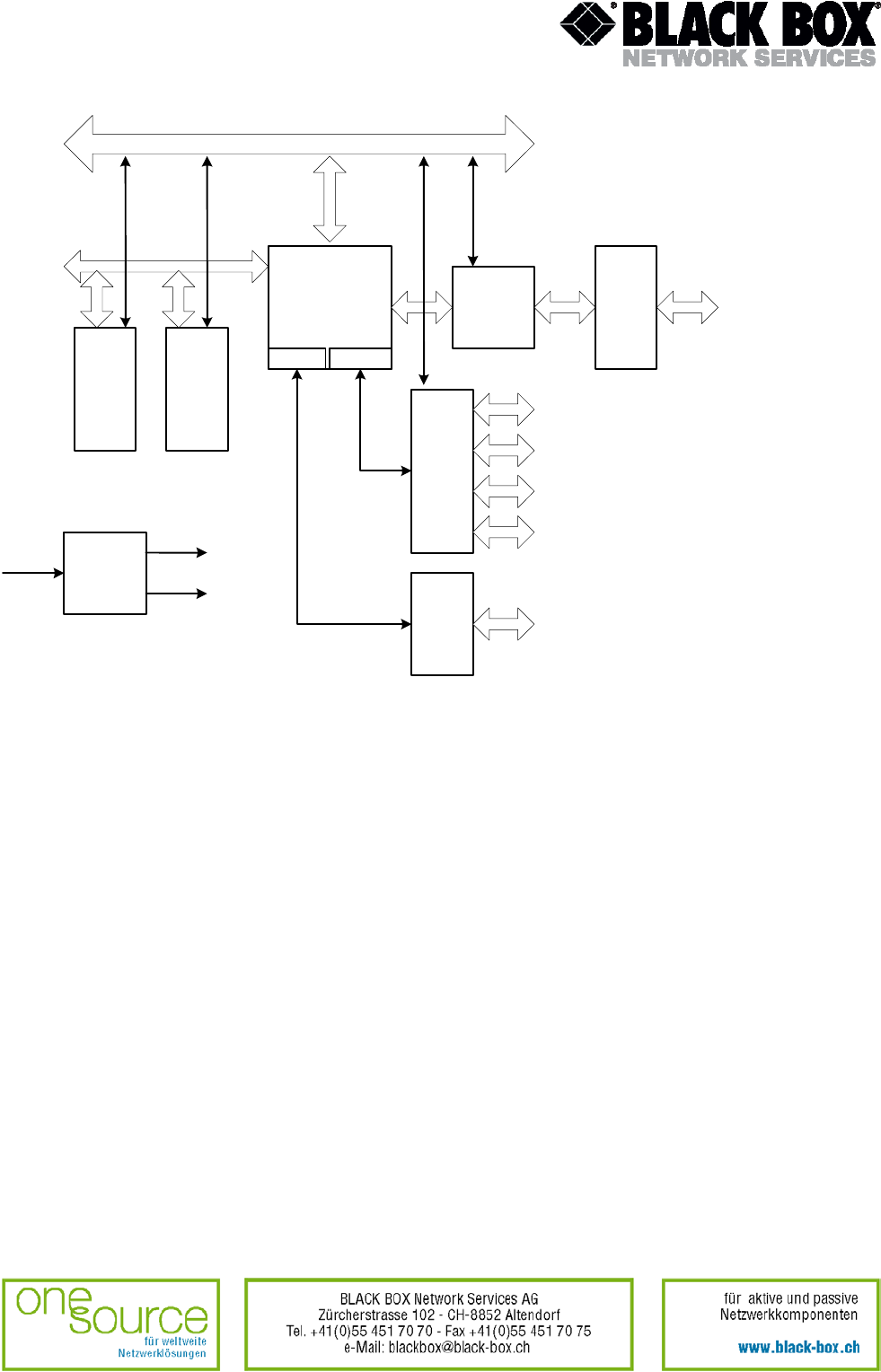

CPU

ROMRAM

EthernetRS-232

DSP

A

FT

To

DSL

line

Ether-

net

10

BaseT

RS-

232

Monitor

DC/DC

12 V

+5 V

+3,3 V

Common Bus

Fig. 15 Structural schematic of MDS92xxx-10BT

The CPU enables control of all devices’ functioning units in accordance with the firmware and the

parameters configured. The CPU supports the Ethernet and RS-232 interfaces.

The memory unit keeps the control micro program, temporary values and buffers Ethernet

packets.

The setup of the parameters, mode switching and system control are enabled though the

management interface with the help of VT-100-type terminal or over Telnet and HTTP protocols

through Ethernet. The firmware loading can be implemented through the Ethernet interface as

well.

The signal processor enables translation of data flow before it is transmitted over a line. The

signal processor also enables:

• structure generation of the SHDSL cycle (word synchronization, bits, etc.) and its filling with

data:

• synchronization flattening between the internal bus of the device and transmission on the line

(i.e. management of the stuffing algorithm).

The signal processor also controls the process of communication on lines and digital processing

Version: 1.0 Page. 32 of 95