4–32 Cache and External Interfaces

21264/EV68A Hardware Reference Manual

System Port

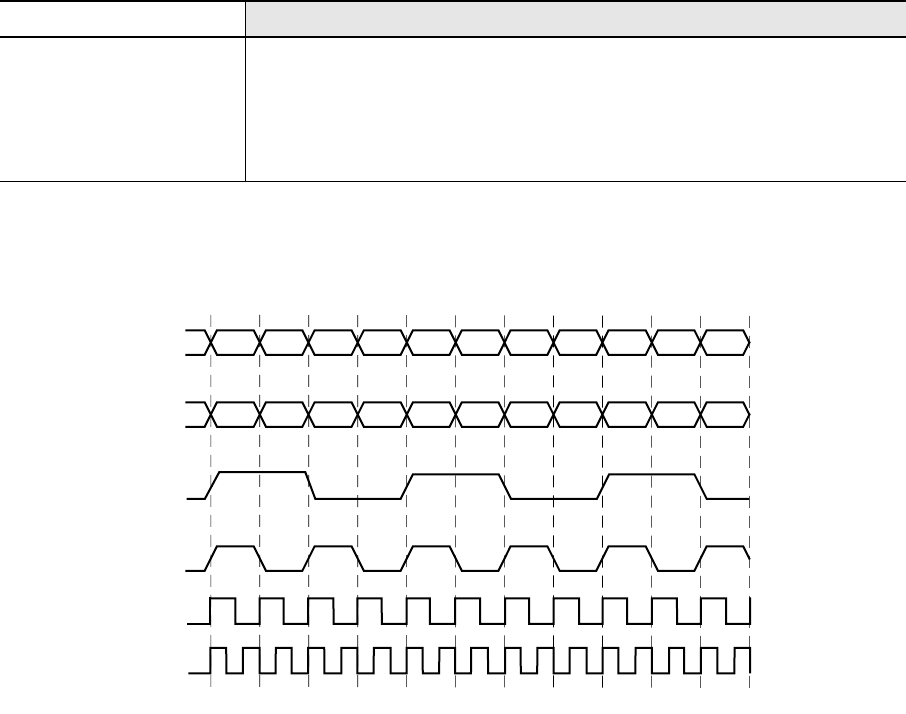

Figure 4–5 show a simple example of a fast transfer. The data rate ratio is 1.5X with a

4:1 SYSCLK to INT_FWD_CLK ratio.

Figure 4–5 Fast Transfer Timing Example

In fast data mode, movement of data into the 21264/EV68A requires turning around the

SysData bus that is being actively driven by the 21264/EV68A. Given a SysDc fill

command (ReadDataError, ReadData, ReadDataShared, ReadDataShared/Dirty, Read-

DataDirty), the 21264/EV68A responds as follows:

1. Three GCLK cycles after perceiving the SysDc fill command, the 21264/EV68A

turns off its drivers, interrupting any ongoing fast data write transactions.

2. The 21264/EV68A drivers stay off until the last piece of fill data is received, or a

new SysDc write command overrides the current SysDc fill command. It is the

responsibility of the external system to schedule SysDc fill or write commands so

that there is no conflict on the SysData bus.

3. The 21264/EV68A samples fill data in the GCLK clock domain, 10 +

SYSDC_DELAY GCLK cycles after perceiving the SysDc fill command. The

Cbox CSR SYSDC_DELAY[4:0] provides GCLK granularity for precisely placing

fills into the processor pipeline discussed in Section 2.2.

Table 4–25 SYSCLK Cycles Between SysAddOut and SysData

GCLK/INT_FWD_CLK (Data Rate Ratio)

System framing clock ratio 1.5X 2.0X 2.5X 3.0X 3.5X 4.0X 5.0X 6.0X 7.0X 8.0X

1 4 32 2 2 21111

2 2 21 1 1 11111

4 1 11 1 1 11111

FM05822B.AI4

SysData_L[63:0]

SYSCLK

Probe

SysAddOut_L[14:0]

SysAddOutClk_L

D0

Response

D1 D2 D3 D4 D5 D6

INT_FWD_CLK

GCLK