2–24 Internal Architecture

21264/EV68A Hardware Reference Manual

Special Cases of Alpha Instruction Execution

2.6.3 Prefetch, Evict Next: LDQ and HW_LDQ Instructions

The 21264/EV68A processes this instruction like a normal prefetch transaction (Read-

BlkSpec command), with one exception—if the load misses the Dcache, the addressed

cache block is allocated into the Dcache, but the Dcache set allocation pointer is left

pointing to this block. The next miss to the same Dcache line will evict the block. For

example, this instruction might be used when software is reading an array that is known

to fit in the offchip Bcache, but will not fit into the onchip Dcache. In this case, the

instruction ensures that the hardware provides the desired prefetch function without dis-

placing useful cache blocks stored in the other set within the Dcache.

The HW_LDQ instruction construct equates to the HW_LD instruction with the LEN

field set. See Table 6–3.

2.7 Special Cases of Alpha Instruction Execution

This section describes the mechanisms that the 21264/EV68A uses to process irregular

instructions in the Alpha instruction set, and cases in which the 21264/EV68A pro-

cesses instructions in a non-intuitive way.

2.7.1 Load Hit Speculation

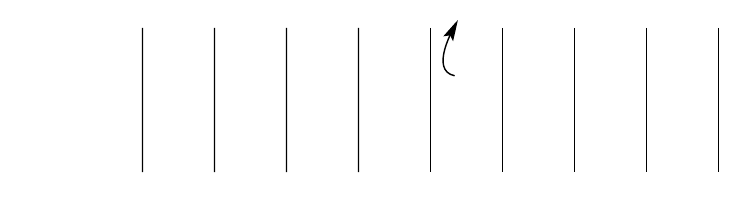

The latency of integer load instructions that hit in the Dcache is three cycles. Figure 2–

9 shows the pipeline timing for these integer load instructions. In Figure 2–9:

Figure 2–9 Pipeline Timing for Integer Load Instructions

There are two cycles in which the IQ may speculatively issue instructions that use load

data before Dcache hit information is known. Any instructions that are issued by the IQ

within this 2-cycle speculative window are kept in the IQ with their requests inhibited

until the load instruction’s hit condition is known, even if they are not dependent on the

load operation. If the load instruction hits, then these instructions are removed from the

queue. If the load instruction misses, then the execution of these instructions is aborted

and the instructions are allowed to request service again.

Symbol Meaning

Q Issue queue

R Register file read

EExecute

D Dcache access

BDatabusactive

1Cycle Number

ILD

Instruction 1

Instruction 2

2 3 4 5 6 7 8

QREDB

QR

Q

Hit

FM-05814.AI4