8: Coprocessor Interface

8-2 EPSON ARM720T CORE CPU MANUAL

The coprocessor:

1 Decodes instructions to determine whether it can accept the

instruction.

2 Indicates whether it can accept the instruction (by signaling

on EXTCPA and EXTCPB).

3 Fetches any values required from its own register bank.

4 Performs the operation required by the instruction.

If a coprocessor cannot execute an instruction, the instruction takes the undefined instruction

trap. You can choose whether to emulate coprocessor functions in software, or to design a

dedicated coprocessor.

8.1.1 Coprocessor availability

You can connect up to 16 coprocessors into a system, each with a unique coprocessor ID

number.

Some coprocessor numbers are reserved. For example, you cannot assign external

coprocessors to coprocessor numbers 14 and 15, because these are internal to the ARM720T

processor:

• CP14 is the communications channel coprocessor

• CP15 is the system control coprocessor for cache and MMU functions.

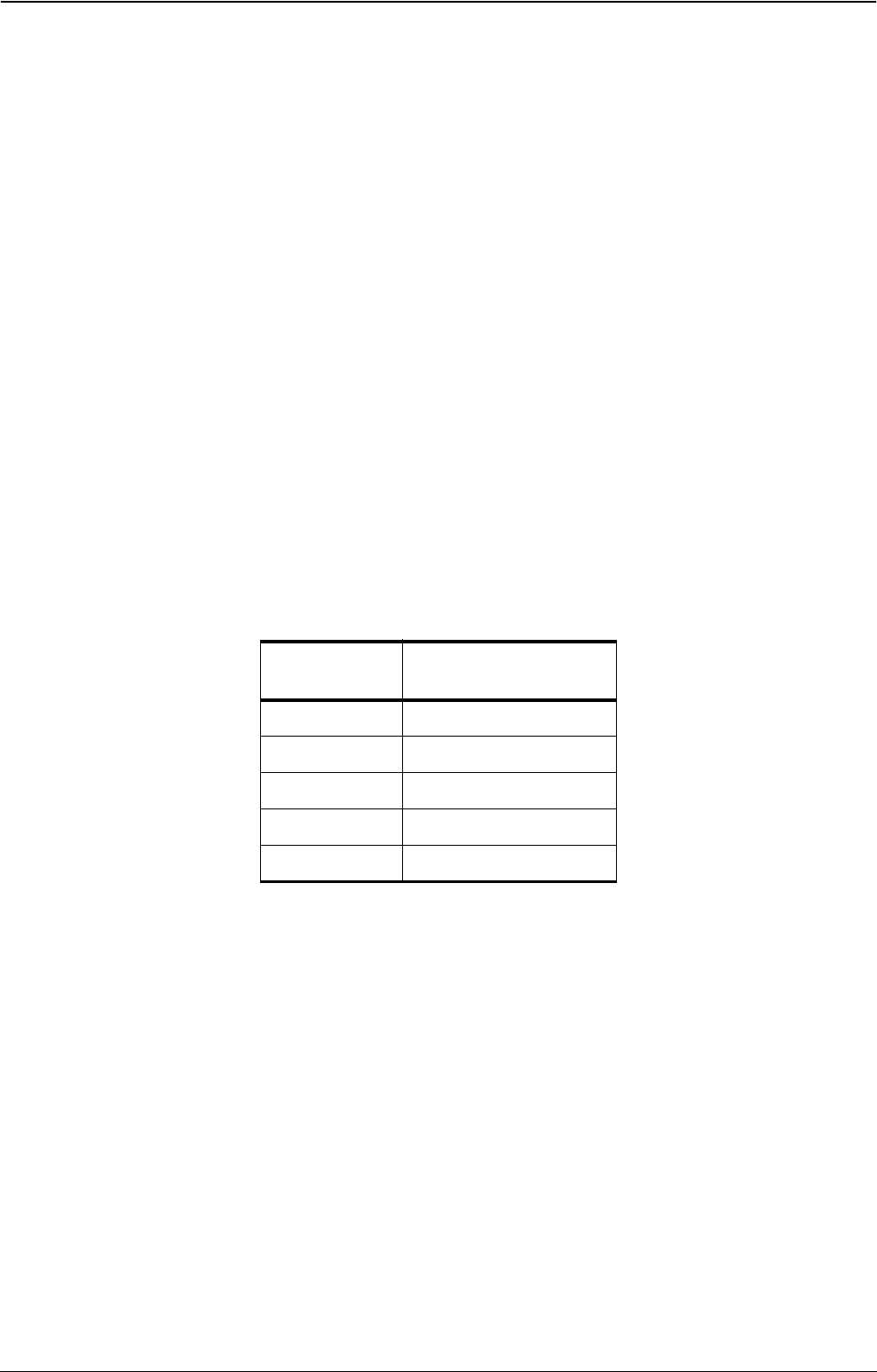

Coprocessor availability is shown in Table 8-1.

Note: If you intend to design a coprocessor, send an E-mail with coprocessor in the subject

line to info@arm.com for up to date information on coprocessor numbers that have

already been allocated.

Table 8-1 Coprocessor availability

Coprocessor

number

Allocation

15 System control

14 Debug controller

13:8 Reserved

7:4 Available to users

3:0 Reserved