9: Debugging Your System

ARM720T CORE CPU MANUAL EPSON 9-25

During SHIFT-DR, a data value is shifted into the serial register. Bits 32 to 36 specify the

address of the EmbeddedICE-RT register to be accessed.

During UPDATE-DR, this register is either read or written depending on the value of bit 37

(0 = read, 1 = write). See Figure 9-12 on page 9-34 for more details.

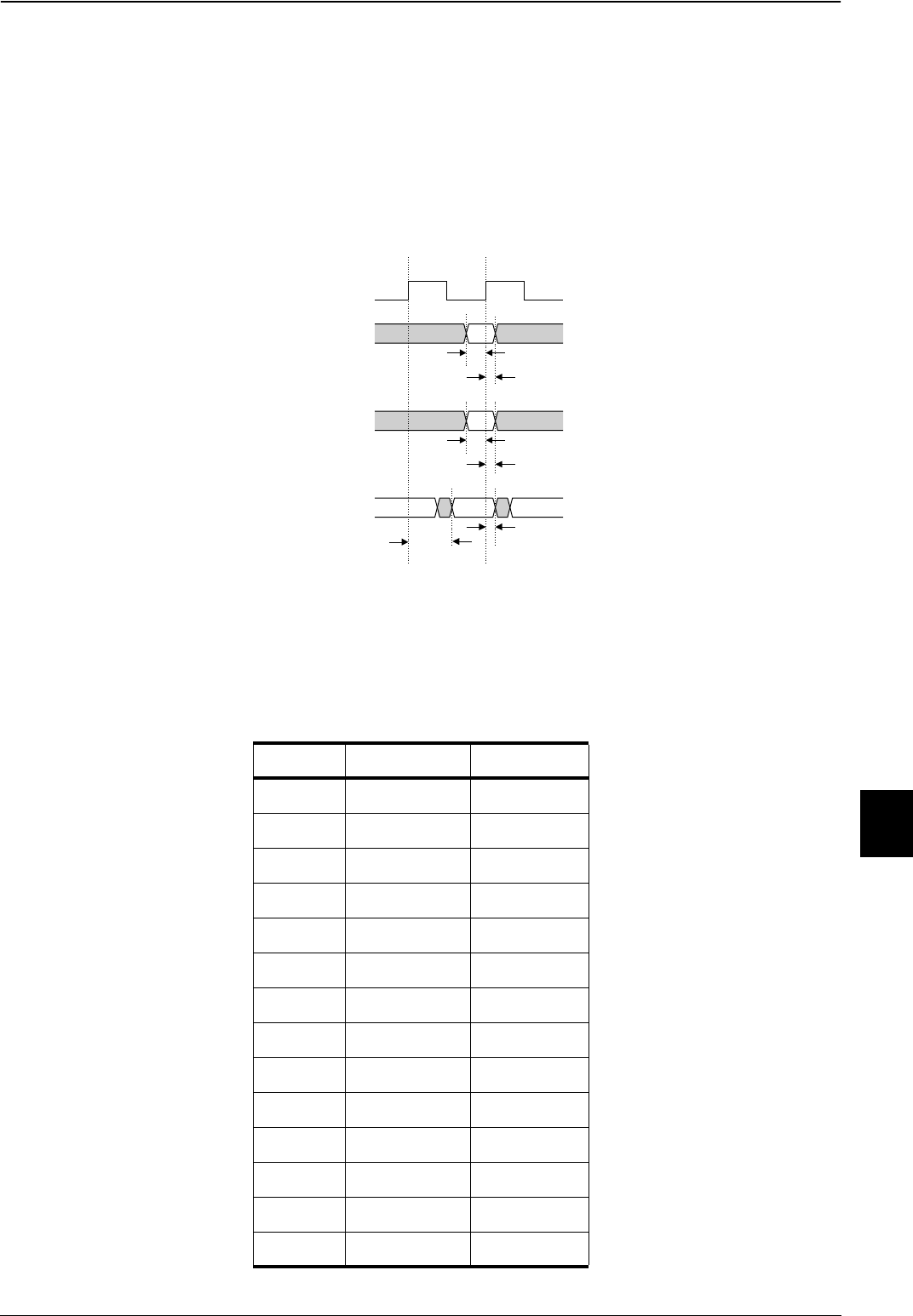

9.15 Scan timing

Figure 9-10 provides general scan timing information.

Figure 9-10 Scan timing

9.15.1 Scan chain 1 cells

The ARM720T processor provides data for scan chain 1 cells as shown in Table 9-6.

Table 9-6 Scan chain 1 cells

Number Signal Type

1 DATA[0] Input/output

2 DATA[1] Input/output

3 DATA[2] Input/output

4 DATA[3] Input/output

5 DATA[4] Input/output

6 DATA[5] Input/output

7 DATA[6] Input/output

8 DATA[7] Input/output

9 DATA[8] Input/output

10 DATA[9] Input/output

11 DATA[10] Input/output

12 DATA[11] Input/output

13 DATA[12] Input/output

14 DATA[13] Input/output

t

ohtdo

t

ovtdo

t

istctl

t

ihtctl

t

istcken

t

ihtcken

HCLK

DBGTCKEN

DBGTMS

DBGTDI

DBGTDO