2: Programmer’s Model

ARM720T CORE CPU MANUAL EPSON 2-5

Interrupt modes

FIQ mode has seven banked registers mapped to r8-14 (r8_fiq-r14_fiq). In ARM state, many

FIQ handlers can use these banked registers to avoid having to save any registers onto a stack.

User, IRQ, Supervisor, Abort, and Undefined modes each have two banked registers, mapped

to r13 and r14, enabling each of these modes to have a private stack pointer and link registers.

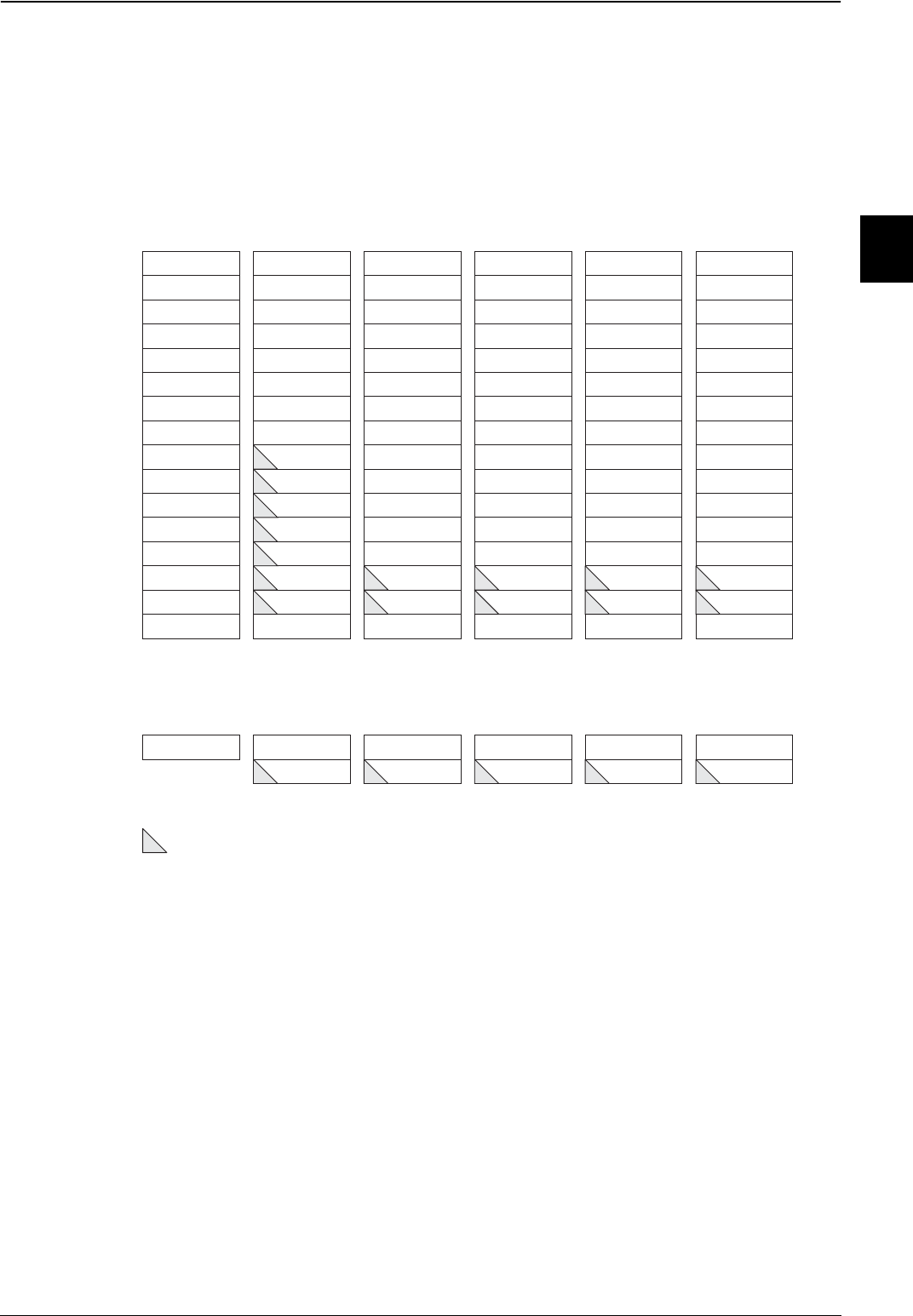

Figure 2-3 Register organization in ARM state

ARM state general registers and program counter

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13

r14

r15 (PC)

System and User

CPSR CPSR

SPSR_fiq

CPSR

SPSR_svc

CPSR

SPSR_abt

CPSR

SPSR_irq

CPSR

SPSR_und

ARM state program status registers

= banked register

r0

r1

r2

r3

r4

r5

r6

r7

r8_fiq

r9_fiq

r10_fiq

r11_fiq

r12_fiq

r13_fiq

r14_fiq

r15 (PC)

FIQ

r0

r1

r2

r3

r4

r5

r6

r7

r13_svc

r14_svc

r15 (PC)

Supervisor

r8

r9

r10

r11

r12

r0

r1

r2

r3

r4

r5

r6

r7

r13_abt

r14_abt

r15 (PC)

Abort

r8

r9

r10

r11

r12

r0

r1

r2

r3

r4

r5

r6

r7

r13_irq

r14_irq

r15 (PC)

IRQ

r8

r9

r10

r11

r12

r0

r1

r2

r3

r4

r5

r6

r7

r13_und

r14_und

r15 (PC)

Undefined

r8

r9

r10

r11

r12