9: Debugging Your System

ARM720T CORE CPU MANUAL EPSON 9-5

9.3 Entry into debug state

If the system is in halt mode, any of the following types of interrupt force the processor into

debug state:

• a breakpoint (a given instruction fetch)

• a watchpoint (a data access)

• an external debug request.

Note: In monitor mode, the processor continues to execute instructions in real time, and

will take an abort exception. The abort status register enables you to establish

whether the exception was due to a breakpoint or watchpoint, or to a genuine

memory abort.

You can use the EmbeddedICE-RT logic to program the conditions under which a breakpoint

or watchpoint can occur. Alternatively, you can use the DBGBREAK signal to enable external

logic to flag breakpoints or watchpoints and monitor the following:

• address bus

• data bus

• control signals.

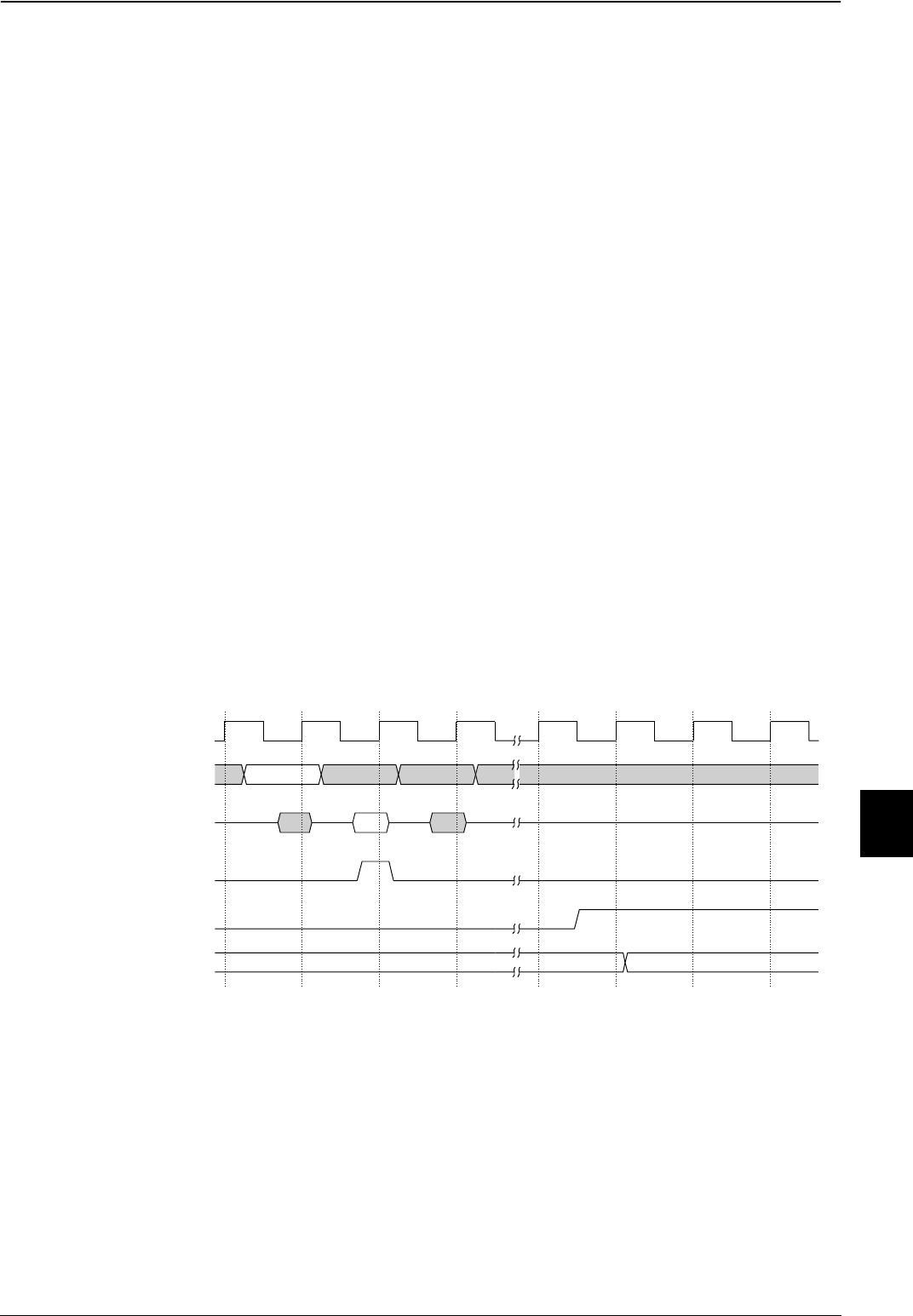

The timing is the same for externally-generated breakpoints and watchpoints. Data must

always be valid around the rising edge of HCLK. When this data is an instruction to be

breakpointed, the DBGBREAK signal must be HIGH around the rising edge of HCLK.

Similarly, when the data is for a load or store, asserting DBGBREAK around the rising edge

of HCLK marks the data as watchpointed.

When a breakpoint or watchpoint is generated, there might be a delay before the ARM720T

core enters debug state. When it enters debug state, the DBGACK signal is asserted. The

timing for an externally-generated breakpoint is shown in Figure 9-3.

Figure 9-3 Debug state entry

HCLK

Internal cyclesMemory cycles

HADDR[31:0]

DBGACK

DATA[31:0]

DBGBREAK

HTRANS[1:0]