2: Programmer’s Model

ARM720T CORE CPU MANUAL EPSON 2-9

2.7.3 Reserved bits

The remaining bits in the PSRs are reserved. When changing flag or control bits of a PSR, you

must ensure that these unused bits are not altered. Also, your program must not rely on them

containing specific values, because in future processors they might read as one or zero.

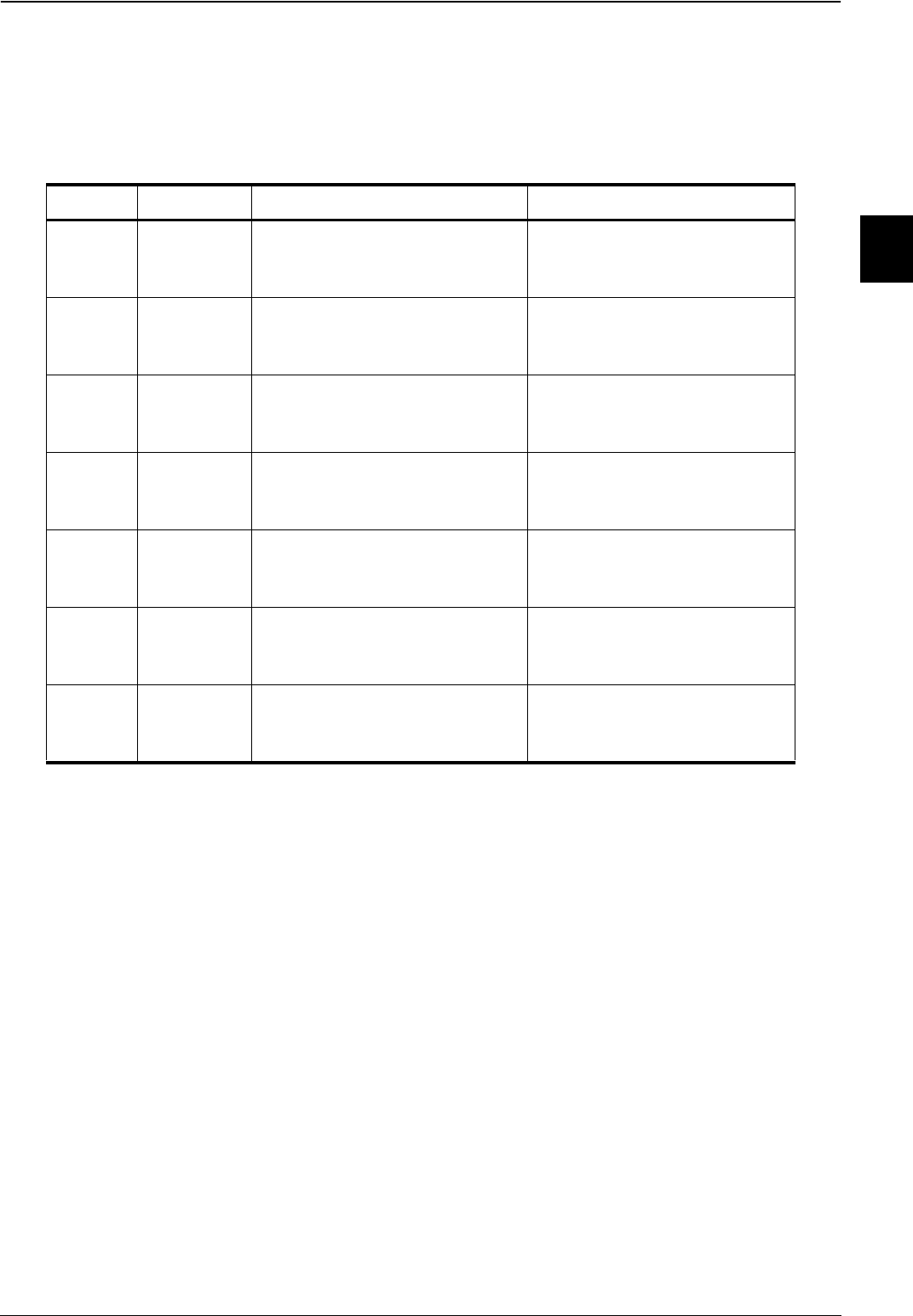

Table 2-2 PSR mode bit values

M[4:0] Mode Visible Thumb state registers Visible ARM state registers

b10000 User r7 to r0,

LR, SP

PC, CPSR

r14 to r0,

PC, CPSR

b10001 FIQ r7 to r0,

LR_fiq, SP_fiq

PC, CPSR, SPSR_fiq

r7 to r0,

r14_fiq..r8_fiq,

PC, CPSR, SPSR_fiq

b10010 IRQ r7 to r0,

LR_irq, SP_irq

PC, CPSR, SPSR_irq

r12 to r0,

r14_irq, r13_irq,

PC, CPSR, SPSR_irq

b10011 Supervisor r7 to r0,

LR_svc, SP_svc,

PC, CPSR, SPSR_svc

r12 to r0,

r14_svc, r13_svc,

PC, CPSR, SPSR_svc

b10111 Abort r7 to r0,

LR_abt, SP_abt,

PC, CPSR, SPSR_abt

r12 to r0,

r14_abt..r13_abt,

PC, CPSR, SPSR_abt

b11011 Undefined r7 to r0

LR_und, SP_und,

PC, CPSR, SPSR_und

r12 to r0,

r14_und, r13_und,

PC, CPSR, SPSR_und

b11111 System r7 to r0,

LR, SP

PC, CPSR

r14 to r0,

PC, CPSR