3: Configuration

3-2 EPSON ARM720T CORE CPU MANUAL

3.2 Internal coprocessor instructions

The instruction set for the ARM720T processor enables you to implement specialized

additional instructions using coprocessors. These are separate processing units that are

coupled to the ARM720T processor, although CP15 is built into the ARM720T processor.

Note: The CP15 register map might change in future ARM processors. You are strongly

recommended to structure software so that any code accessing CP15 is contained in

a single module, enabling it to be easily updated.

You can only access CP15 registers with MRC and MCR instructions in a privileged mode. The

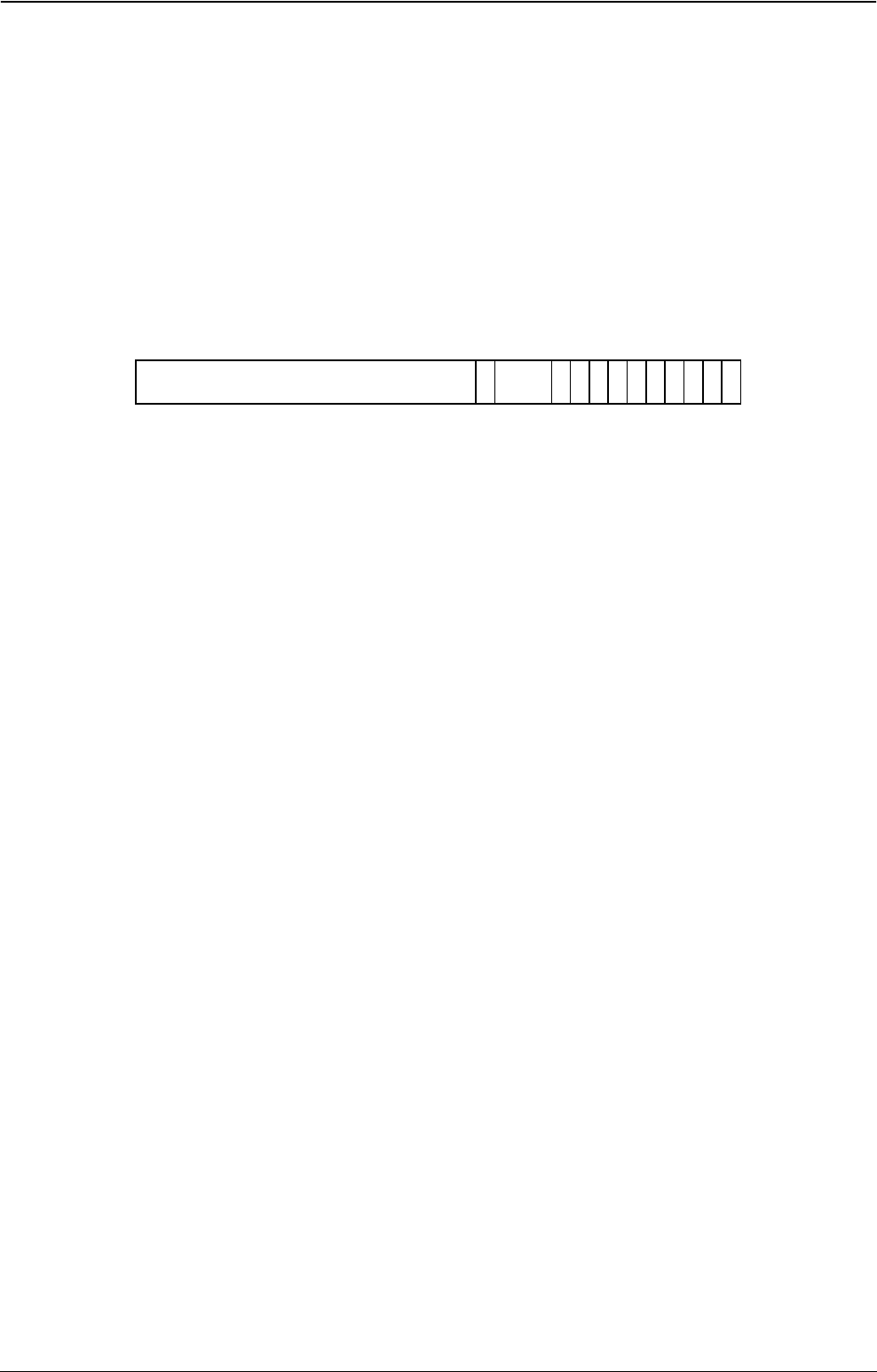

instruction bit pattern of the MRC and MCR instructions is shown in Figure 3-1.

Figure 3-1 MRC and MCR bit pattern

CDP, LDC, and STC instructions, as well as unprivileged

MRC and MCR instructions to CP15 cause the Undefined Instruction trap to be taken.

The CRn field of MRC and MCR instructions specifies the coprocessor register to access. The

CRm field and opcode_2 fields specify a particular action when addressing some registers.

In all instructions accessing CP15:

• the opcode_1 field Should Be Zero (SBZ)

• the opcode_2 and CRm fields Should Be Zero except when accessing registers 7, 8,

and 13 when the specified values must be used to select the desired cache, TLB, or

process identifier operations.

31 14 13 12 10 09 08 07 06 05 04 03 02 01 00

UNP V UNP R S B L D P W C A M