1: Introduction

1-10 EPSON ARM720T CORE CPU MANUAL

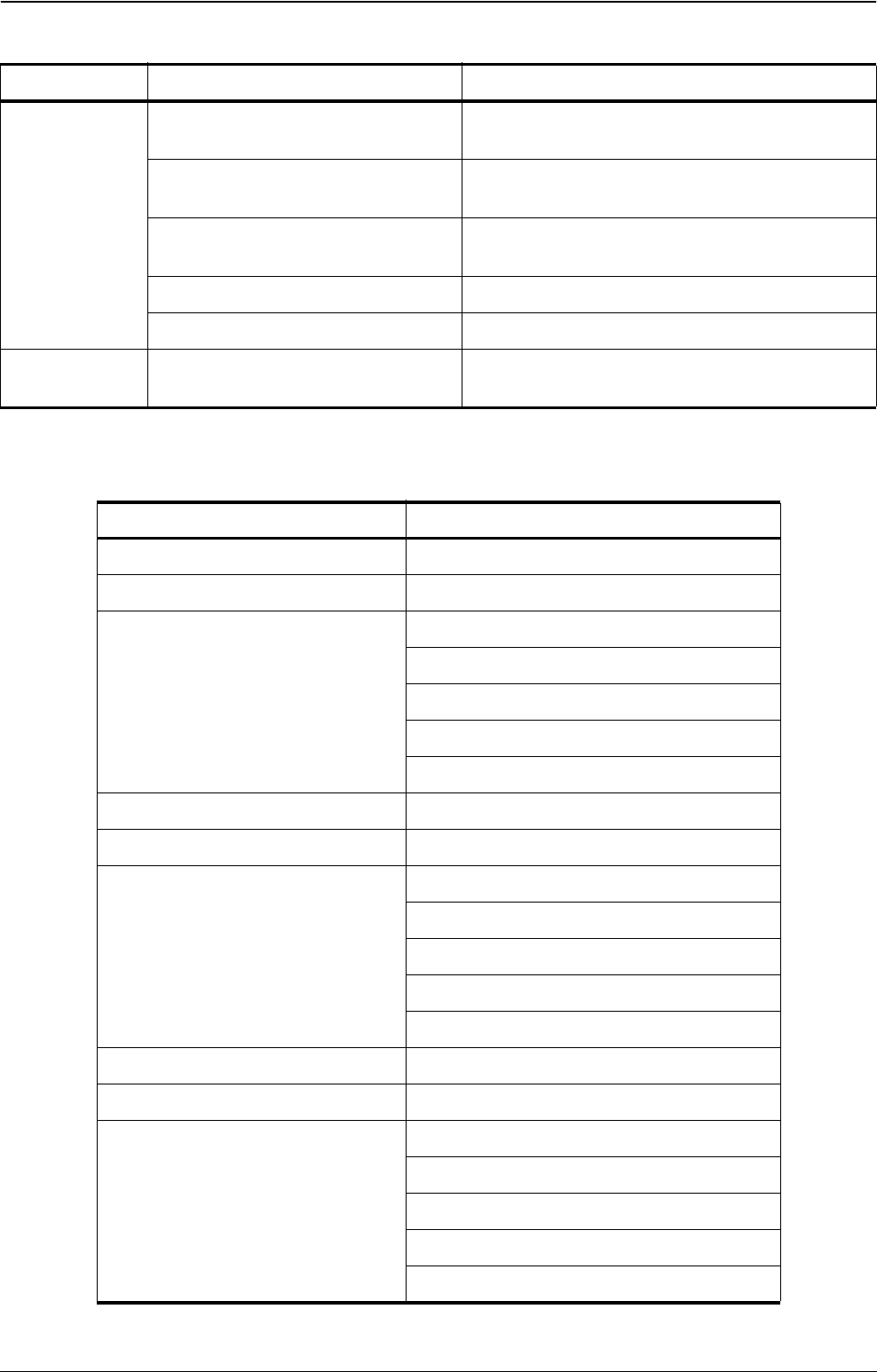

Addressing mode 2, <a_mode2>, is shown in Table 1-3.

Coprocessors Data operations CDP{cond} p<cpnum>, <op1>, <CRd>, <CRn>,

<CRm>, <op2>

Move to ARM reg from coproc MRC{cond} p<cpnum>, <op1>, <Rd>, <CRn>,

<CRm>, <op2>

Move to coproc from ARM reg MCR{cond} p<cpnum>, <op1>, <Rd>, <CRn>,

<CRm>, <op2>

Load LDC{cond} p<cpnum>, <CRd>, <a_mode5>

Store STC{cond} p<cpnum>, <CRd>, <a_mode5>

Software

Interrupt

SWI <24bit_Imm>

Table 1-3 Addressing mode 2

Operation Assembler

Immediate offset [<Rn>, #+/-<12bit_Offset>]

Register offset [<Rn>, +/-<Rm>]

Scaled register offset [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, RRX]

Pre-indexed immediate offset [<Rn>, #+/-<12bit_Offset>]!

Pre-indexed register offset [<Rn>, +/-<Rm>]!

Pre-indexed scaled register offset [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, RRX]!

Post-indexed immediate offset [<Rn>], #+/-<12bit_Offset>

Post-indexed register offset [<Rn>], +/-<Rm>

Post-indexed scaled register offset [<Rn>], +/-<Rm>, LSL #<5bit_shift_imm>

[<Rn>], +/-<Rm>, LSR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ASR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ROR #<5bit_shift_imm>

[<Rn>, +/-<Rm>, RRX]

Table 1-2 ARM instruction summary (continued)

Operation Assembler