A: Signal Descriptions

ARM720T CORE CPU MANUAL EPSON A-5

A.5 Embedded trace macrocell interface signals

The ETM interface signals are shown in Table A-5.

DBGRNG[1:0] Output Range out.

These signals indicate that the relevant EmbeddedICE-RT watchpoint

register has matched the conditions currently present on the address,

data, and control buses. These signals are independent of the state of

the watchpoint enable control bits.

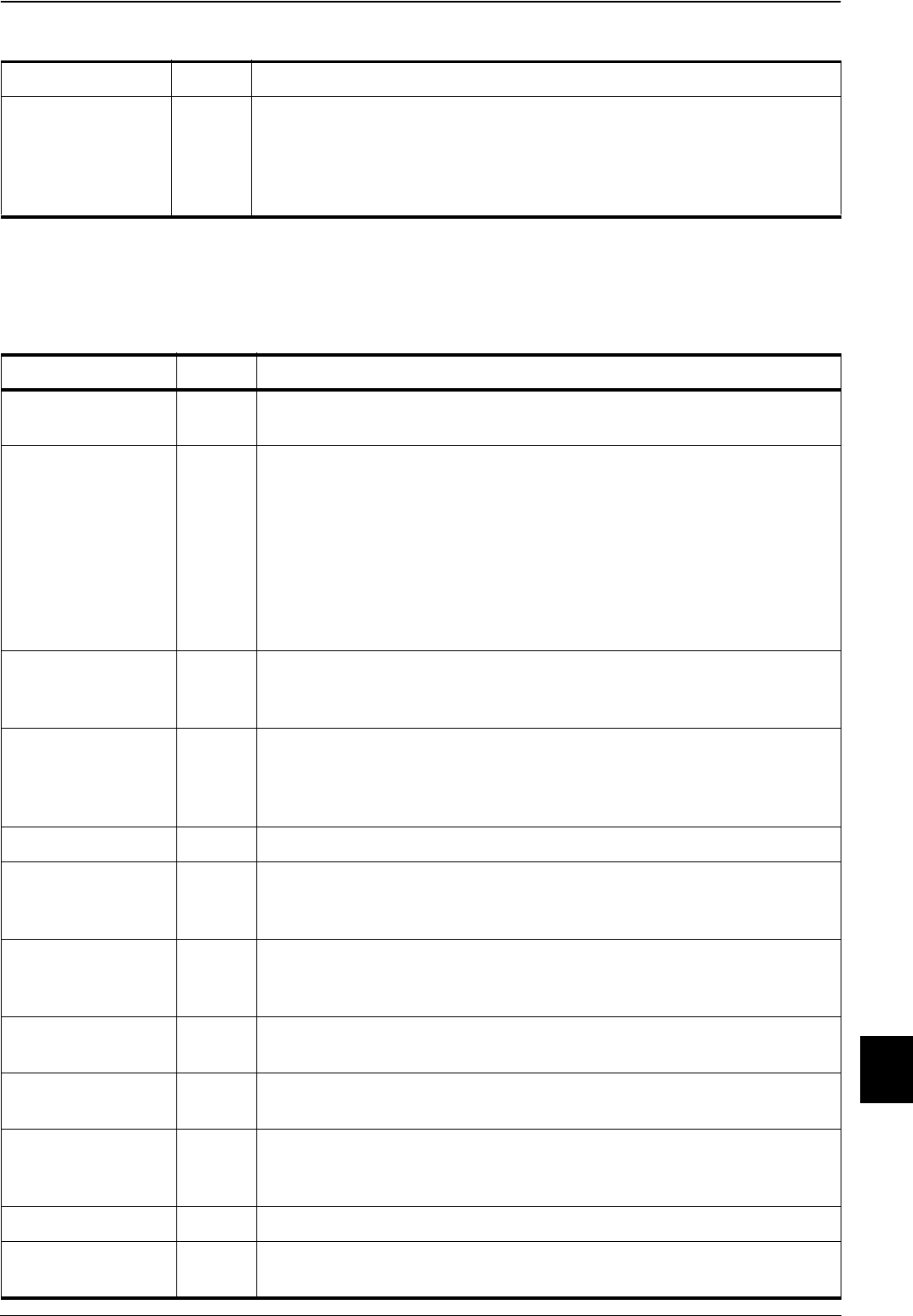

Table A-5 ETM interface signal descriptions

Output name Type Description

ETMnMREQ Output Not memory request. When LOW, indicates that the processor requires

memory access during the following cycle.

ETMSEQ Output Sequential address. When HIGH, indicates that the address of the next

memory cycle is related to that of the last memory cycle. The new

address is one of the following:

• the same as the previous one

• four greater in ARM state

• two greater in Thumb state.

This signal can be used, with the low order address lines, to indicate

that the next cycle can use a fast memory mode and bypass the

address translation system.

ETMnEXEC Output Not executed. When HIGH, indicates that the instruction in the

execution unit is not being executed. For example it might have failed

the condition check code.

ETMnCPI Output Not coprocessor instruction. When the ARM720T processor executes a

coprocessor instruction, it takes the ETMnCPI LOW and waits for a

response from the coprocessor. The actions taken depend on this

response, which the coprocessor signals on the CPA and CPB inputs.

ETMADDR[31:0] Output Addresses. This is the retimed internal address bus.

ETMnOPC Output Not opcode fetch. When LOW, indicates that the processor is fetching

an instruction from memory. When HIGH, indicates that data, if present,

is being transferred.

ETMDBGACK Output Debug acknowledge. When HIGH, indicates that the processor is in

debug state. When LOW, indicates that the processor is in normal

system state.

ETMABORT Output Memory abort or bus error. Indicates that a requested access has been

disallowed.

ETMCPA Output Coprocessor absent handshake. The coprocessor absent signal. It is a

buffered version of the coprocessor absent signal.

ETMCPB Output Coprocessor busy handshake.

The coprocessor busy signal. It is a buffered version of the coprocessor

absent signal.

ETMPROCID[31:0] Output Trace PROCID bus.

ETMPROCIDWR Output Trace PROCID write. Indicates to the ETM7 that the Trace PROCID,

CP15 register c13, has been written.

Table A-4 Debugger signal descriptions

Name Type Description