1: Introduction

1-8 EPSON ARM720T CORE CPU MANUAL

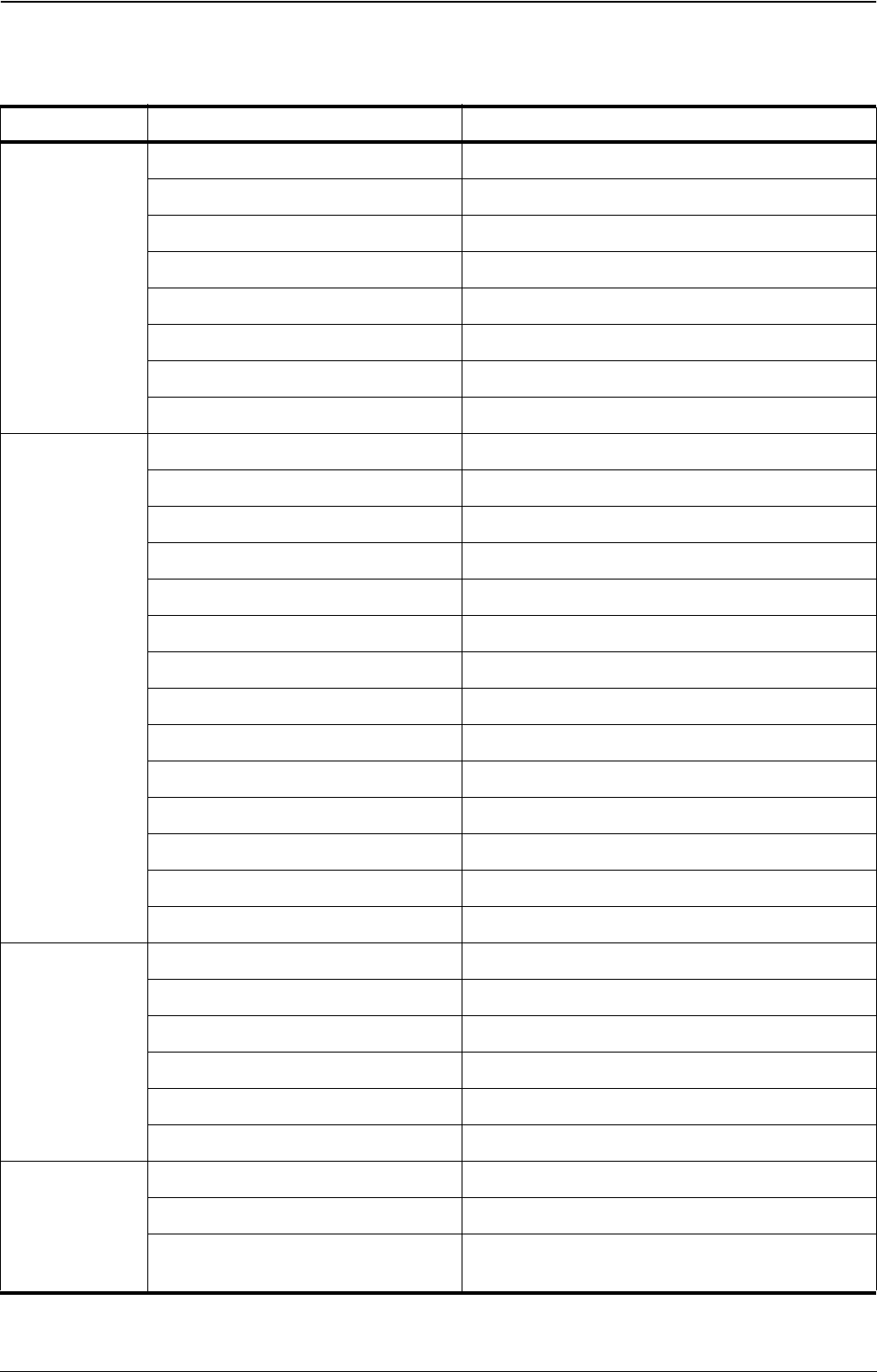

The ARM instruction set summary is shown in Table 1-2.

Table 1-2 ARM instruction summary

Operation Assembler

Move Move MOV{cond}{S} <Rd>, <Oprnd2>

Move NOT MVN{cond}{S} <Rd>, <Oprnd2>

Move SPSR to register MRS{cond} <Rd>, SPSR

Move CPSR to register MRS{cond} <Rd>, CPSR

Move register to SPSR MSR{cond} SPSR{field}, <Rm>

Move register to CPSR MSR{cond} CPSR{field}, <Rm>

Move immediate to SPSR flags MSR{cond} SPSR_f, #<32bit_Imm>

Move immediate to CPSR flags MSR{cond} CPSR_f, #<32bit_Imm>

Arithmetic Add ADD{cond}{S} <Rd>, <Rn>, <Oprnd2>

Add with carry ADC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract SUB{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract with carry SBC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract reverse subtract RSB{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract reverse subtract with carry RSC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Multiply MUL{cond}{S} <Rd>, <Rm>, <Rs>

Multiply accumulate MLA{cond}{S} <Rd>, <Rm>, <Rs>, <Rn>

Multiply unsigned long UMULL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Multiply unsigned accumulate long UMLAL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Multiply signed long SMULL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Multiply signed accumulate long SMLAL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Compare CMP{cond} <Rd>, <Oprnd2>

Compare negative CMN{cond} <Rd>, <Oprnd2>

Logical Test TST{cond} <Rn>, <Oprnd2>

Test equivalence TEQ{cond} <Rn>, <Oprnd2>

AND AND{cond}{S} <Rd>, <Rn>, <Oprnd2>

EOR EOR{cond}{S} <Rd>, <Rn>, <Oprnd2>

ORR ORR{cond}{S} <Rd>, <Rn>, <Oprnd2>

Bit clear BIC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Branch Branch B{cond} <label>

Branch with link BL{cond} <label>

Branch, and exchange instruction

set

BX{cond} <Rn>