11: Test Support

ARM720T CORE CPU MANUAL EPSON 11-3

11.3 Test State Register

The test state register contains only one bit, bit 0:

Bit 0 set Enable MMU and cache test.

Bit 0 clear Disable MMU and cache test.

At reset (HRESETn LOW), bit 0 is cleared.

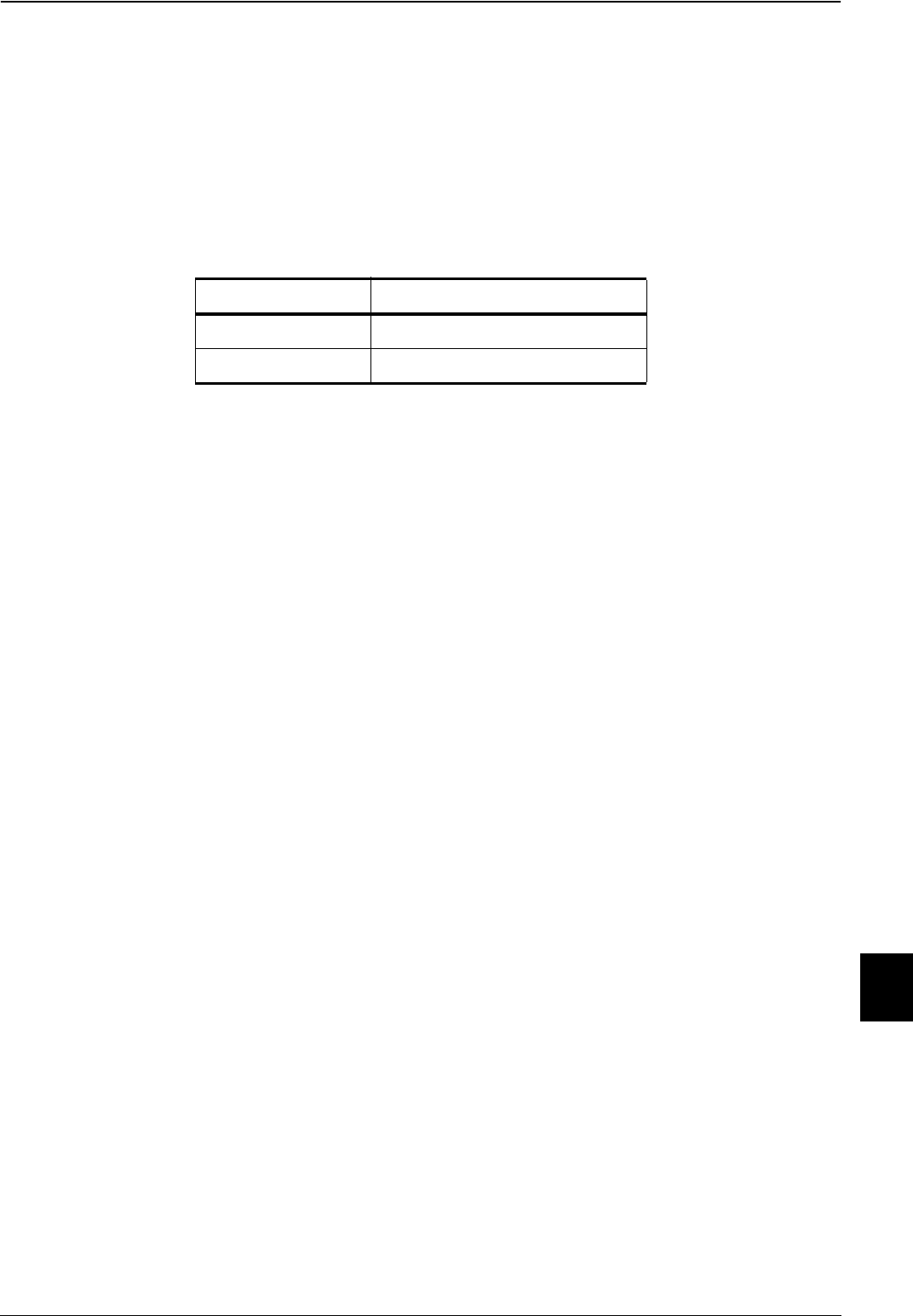

The test state register operations are shown in Table 11-2.

Note: Cache and MMU test operations are only supported when the Test State Register

is on.

11.4 Cache test registers and operations

The cache is maintained using MCR and MRC instructions to CP15 registers c7 and c9,

defined by the ARM v4T programmer’s model. Additional operations are available using MCR

and MRC instructions to CP15 register c15. These operations are combined with those using

registers c7 and c9 to enable testing of the cache entirely in software.

CP15 register c7 is write-only, and provides only one function:

• invalidate cache.

The CP15 register c9 operations are read and write. The operations available are:

• write victim and lockdown base

• write victim.

The CP15 register c15 operations are:

• write to register C15.C

• read from register C15.C

• CAM read to C15.C

• CAM write

• RAM read to C15.C

• RAM write from C15.C

• CAM match, RAM read to C15.C.

Note: For the CAM Match, RAM Read operation the respective MMU does not perform a

lookup and a cache miss does not cause a linefill.

The register c15 operations are all issued as MCR. The Rd field defines the address for the

operation. Therefore, the data is either supplied from, or latched into, CP15.C in CP15. These

32-bit registers are accessed with CP15 MCR and MRC instructions.

Table 11-2 Test State Register operations

Operation Instruction

Write test register MCR p15, 7, <Rd>, c15, c15, 7

Read test register MRC p15, 7, <Rd>, c15, c15, 7