1: Introduction

ARM720T CORE CPU MANUAL EPSON 1-11

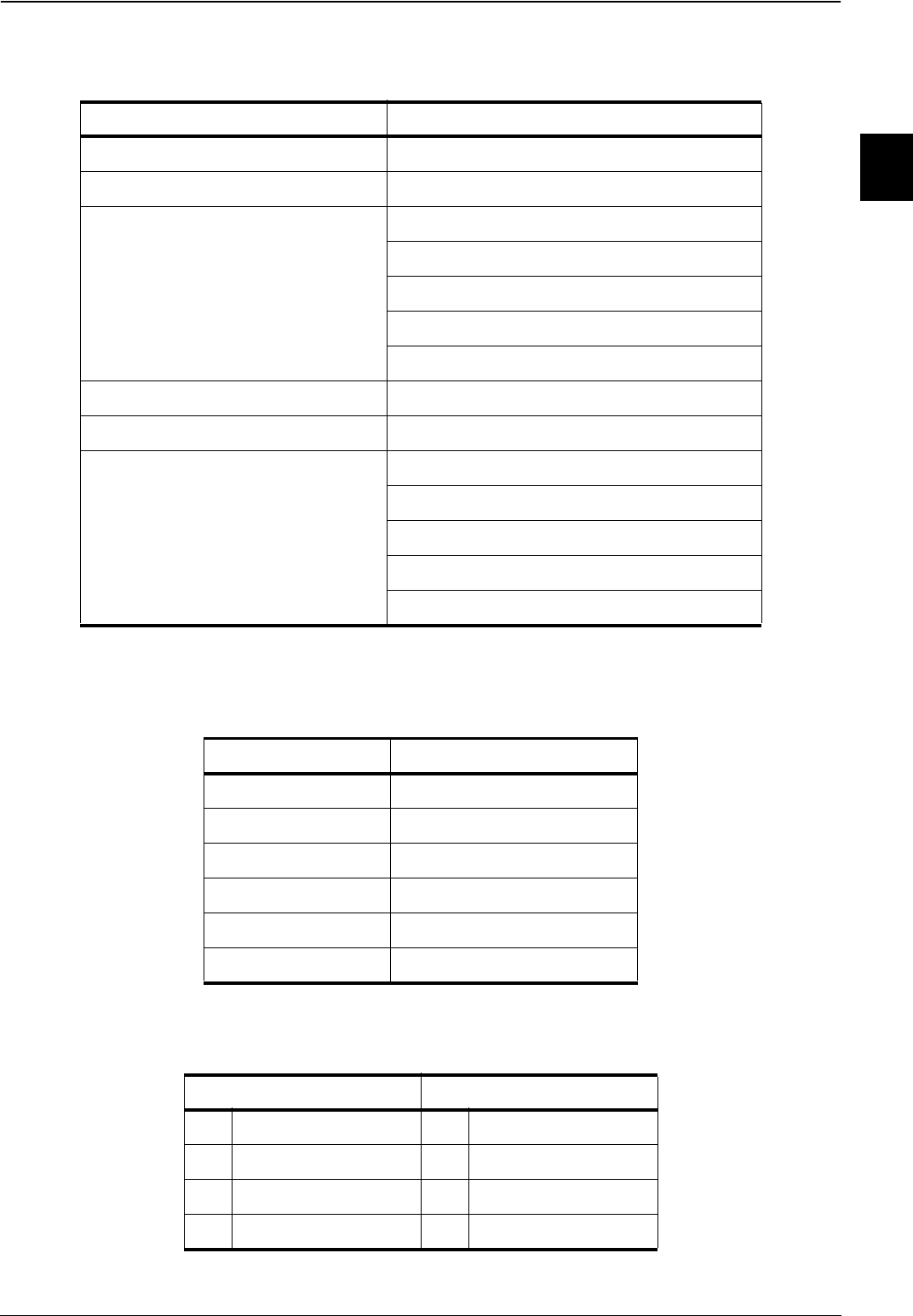

Addressing mode 2 (privileged), <a_mode2P>, is shown in Table 1-4.

Addressing mode 3 (signed byte, and halfword data transfer), <a_mode3>, is shown in

Table 1-5.

Addressing mode 4 (load), <a_mode4L>, is shown in Table 1-6.

Table 1-4 Addressing mode 2 (privileged)

Operation Assembler

Immediate offset [<Rn>, #+/-<12bit_Offset>]

Register offset [<Rn>, +/-<Rm>]

Scaled register offset [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, RRX]

Post-indexed immediate offset [<Rn>], #+/-<12bit_Offset>

Post-indexed register offset [<Rn>], +/-<Rm>

Post-indexed scaled register offset [<Rn>], +/-<Rm>, LSL #<5bit_shift_imm>

[<Rn>], +/-<Rm>, LSR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ASR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ROR #<5bit_shift_imm>

[<Rn>, +/-<Rm>, RRX]

Table 1-5 Addressing mode 3

Operation Assembler

Immediate offset [<Rn>, #+/-<8bit_Offset>]

Pre-indexed [<Rn>, #+/-<8bit_Offset>]!

Post-indexed [<Rn>], #+/-<8bit_Offset>

Register [<Rn>, +/-<Rm>]

Pre-indexed [<Rn>, +/-<Rm>]!

Post-indexed [<Rn>], +/-<Rm>

Table 1-6 Addressing mode 4 (load)

Addressing mode Stack type

IA Increment after FD Full descending

IB Increment before ED Empty descending

DA Decrement after FA Full ascending

DB Decrement before EA Empty ascending