6: The Bus Interface

6-8 EPSON ARM720T CORE CPU MANUAL

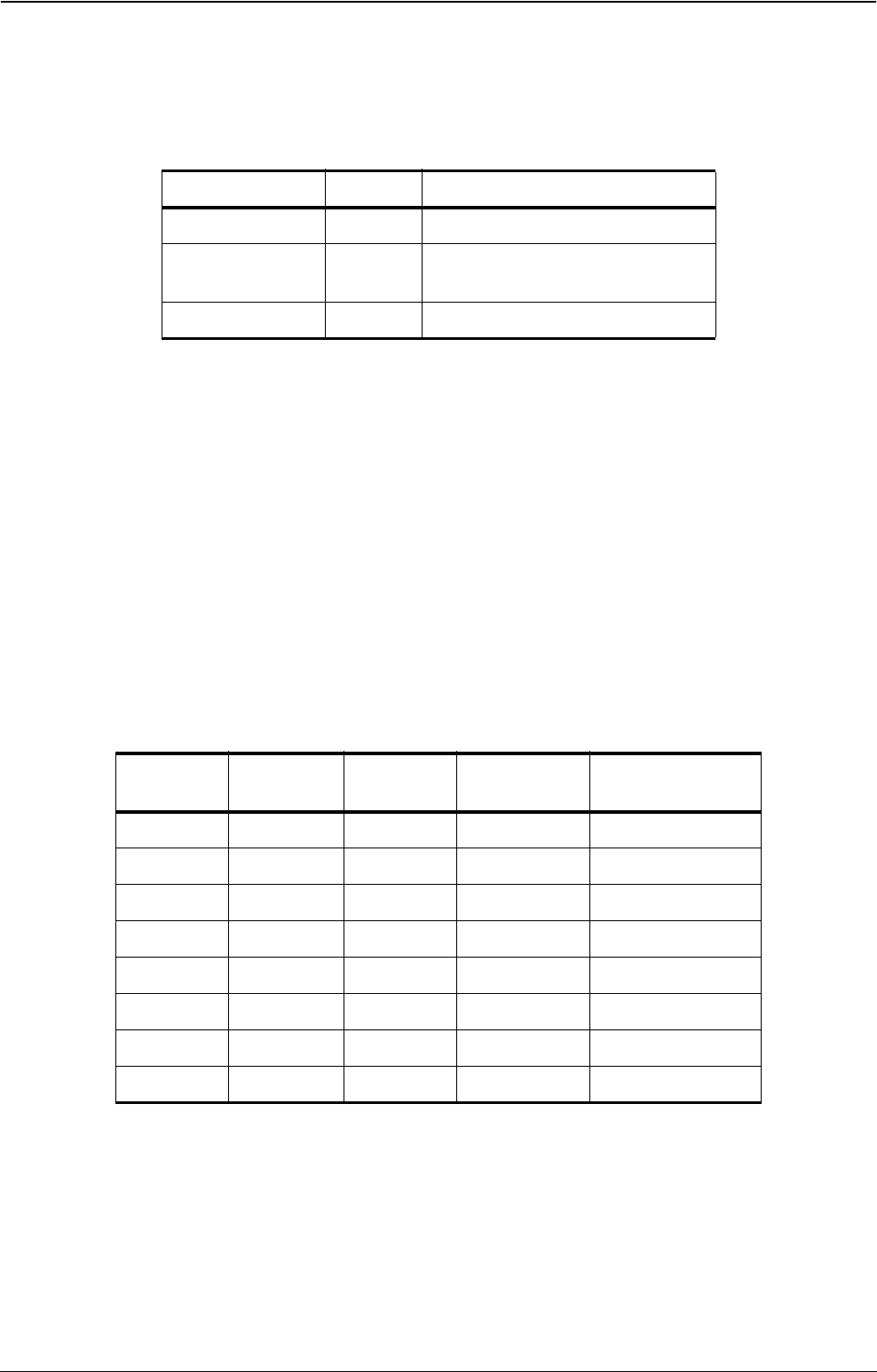

6.4.4 HBURST[2:0]

HBURST[2:0] indicates the type of burst generated by the ARM720T core, as shown in

Table 6-3.

For more details of burst operation, see the

AMBA Specification (Rev 2.0)

.

6.4.5 HPROT[3:0]

HPROT[3:0] is the protection control bus. These signals provide additional information about

a bus access and are primarily intended to enable a module to implement an access permission

scheme.

These signals indicate whether the transfer is:

• an opcode fetch or data access

• a privileged-mode access or User-mode access.

For bus masters with a memory management unit, these signals also indicate whether the

current access is cachable or bufferable.

Table 6-4 shows the protection control encodings as produced from the ARM720T core.

Some bus masters are not capable of generating accurate protection information, so it is

recommended that slaves do not use the HPROT[3:0] signals unless strictly necessary.

Table 6-3 Burst type encodings

HBURST[2:0] Type Description

b000 SINGLE Single transfer

b001 INCR Incrementing burst of

unspecified length

b101 INCR8 8-beat incrementing burst

Table 6-4 Protection control encodings

HPROT[3]

cachable

HPROT[2]

bufferable

HPROT[1]

privileged

HPROT[0]

data/opcode

Description

- - - 0 Opcode fetch

- - - 1 Data access

- - 0 - User access

- - 1 - Privileged access

- 0 - - Not bufferable

- 1 - - Bufferable

0 - - - Not cachable

1- - - Cachable