2: Programmer’s Model

2-4 EPSON ARM720T CORE CPU MANUAL

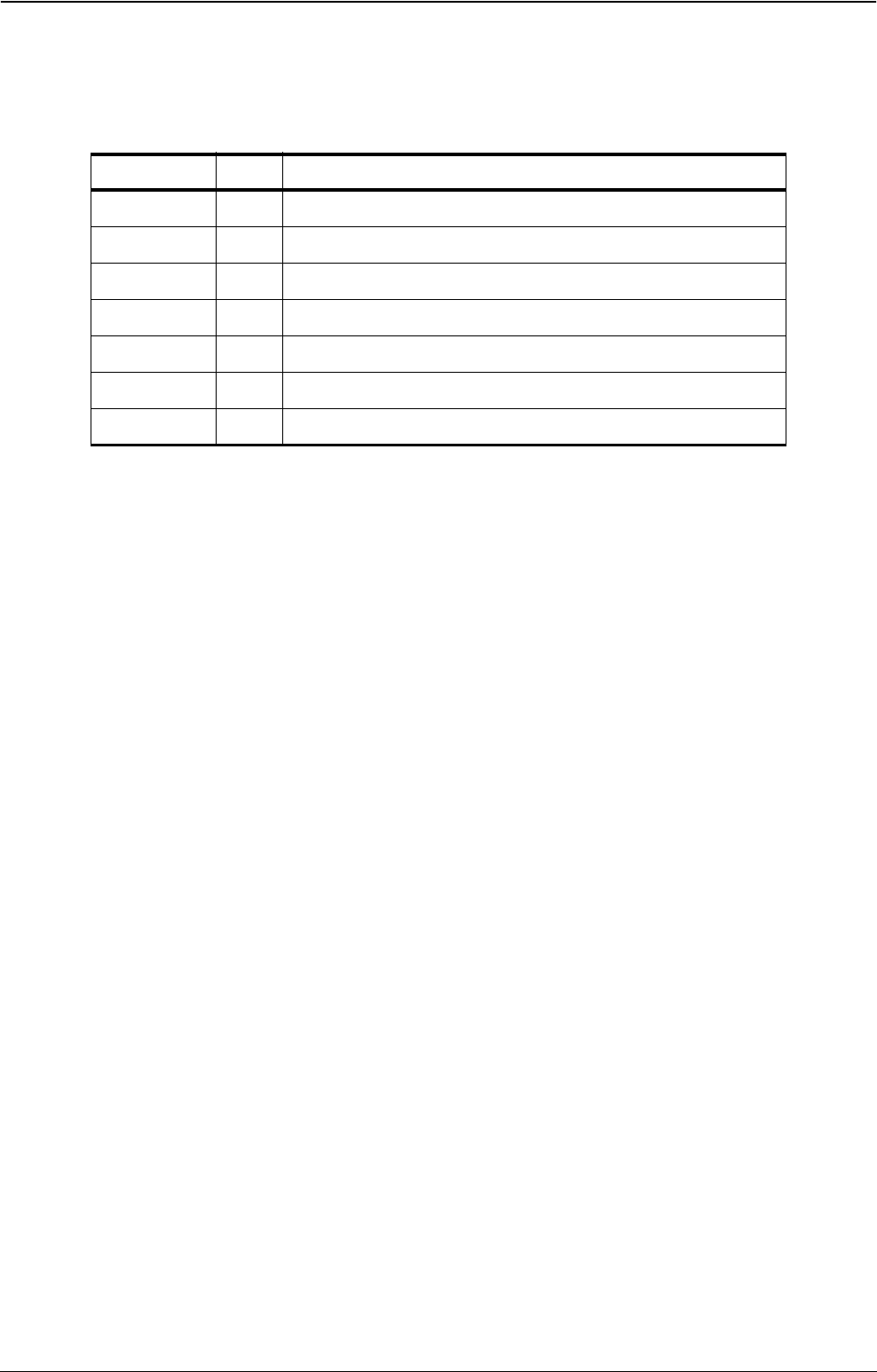

2.5 Operating modes

The ARM720T processor supports seven modes of operation, as shown in Table 2-1.

2.5.1 Changing operating modes

Mode changes can be made under software control, by external interrupts or during exception

processing. Most application programs execute in User mode. The non-User modes, known as

privileged modes, are entered in order to service interrupts or exceptions, or to access

protected resources.

2.6 Registers

The ARM720T processor has a total of 37 registers:

• 31 general-purpose 32-bit registers

• six program status registers.

These registers cannot all be seen at once. The processor state and operating mode dictate

which registers are available to the programmer at any one time.

2.6.1 The ARM state register set

In ARM state, 16 general registers and one or two status registers are visible at any one time.

In privileged (non-User) modes, mode-specific banked registers are switched in. Figure 2-3 on

page 2-5 shows which registers are available in each mode. The banked registers are marked

with a shaded triangle.

The ARM state register set contains 16 directly accessible registers, r0 to r15. All of these,

except r15, are general-purpose, and can be used to hold either data or address values.

Registers r14 and r15 also have special roles, as follows:

Register r14 This register is used as the subroutine Link Register. This receives

a copy of r15 when a

Branch and Link

(BL) code instruction is

executed. At all other times it can be treated as a general-purpose

register. The corresponding banked registers r14_svc, r14_irq,

r14_fiq, r14_abt, and r14_und are similarly used to hold the return

values of r15 when interrupts and exceptions arise, or when BL

instructions are executed within interrupt or exception routines.

Register r15 This register holds the

Program Counter

(PC). In ARM state, bits

[1:0] of r15 are zero and bits [31:2] contain the PC. In Thumb state,

bit 0 is zero and bits [31:1] contain the PC.

In addition to these, the

Current Program Status Register

(CPSR) is used to store status

information. It contains condition code flags and the current mode bits.

Table 2-1 ARM720T modes of operation

Mode Type Description

User usr The normal ARM program execution mode

FIQ fiq Used for most performance-critical interrupts in a system

IRQ irq Used for general-purpose interrupt handling

Supervisor svc Protected mode for the operating system

Abort mode abt Entered after a Data Abort or instruction Prefetch Abort

System sys A privileged User mode for the operating system

Undefined und Entered when an Undefined Instruction is executed