RPM4™ OPERATION AND MAINTENANCE MANUAL

© 2004-2007 DH Instruments, a Fluke Company Page 110

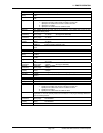

4.5.3 STANDARD EVENT REGISTER

The RPM4 contains an 8 bit Standard event register that reflects specific RPM4 events.

Enabled events in this register will set or clear the ESB bit of the Status Byte Register.

Table 19. 8 Bit Standard Event Register

PON

(128)

URQ

(64)

CMD

(32)

EXE

(16)

DDE

(8)

QYE

(4)

RQC

(2)

OPC

(1)

This register can be read using the “*ESR?” query, Each of these status bits can set the ESB

bit of the Status Byte Register, causing a SRQ to occur IF the ESB bit is enabled to do so.

The Standard Event Status Enable Register (“*ESE” program message ) determines which of

these flags are able to assert the ESB bit. The description of these bits are given as:

PON Power On Bit 7 (128)

Indicates that the RPM4 power has been cycled since the last time this bit was

read or cleared.

URQ User Request Bit 6 (64)

Indicates that the RPM4 was set to local operation manually from the front panel

by the user (pressing the [ESC] key).

CMD Command Error Bit 5 (32)

Indicates that a remote command error has occurred. A command error is

typically a syntax error in the use of a correct program message.

EXE Execution Error Bit 4 (16)

Indicates if a remote program message cannot be processed due to device

related condition.

DDE Device Dependent Error Bit 3 (8)

Indicates that an internal error has occurred in the RPM4 such as a transducer time-

out.

QYE Query Error Bit 2 (4)

Indicates that an error has occurred in the protocol for program message

communications. This is typically caused by a program message being sent to

the RPM4 without reading a waiting reply.

RQC Request Control Bit 1 (2)

This bit is not supported as the RPM4 cannot become the active controller in charge.

OPC Operation Complete Bit 0 (1)

Indicates that the RPM4 has completed all requested functions.

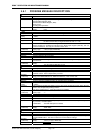

4.5.4 READY STATUS REGISTER

The RPM4 contains an 8 bit Ready Status Register that reflects specific RPM4 Q-RPT

measurement ready events. Enabled events in this register will set or clear the RSB bit of

the Status Byte Register.

Table 20. 8 Bit Ready Status Register

N/A

(128)

MEAS

LO

(64)

NRDY

LO

(32)

RDY

LO

(16)

N/A

(8)

MEAS

HI

(4)

NRDY

HI

(2)

RDY

HI

(1)