Intel

®

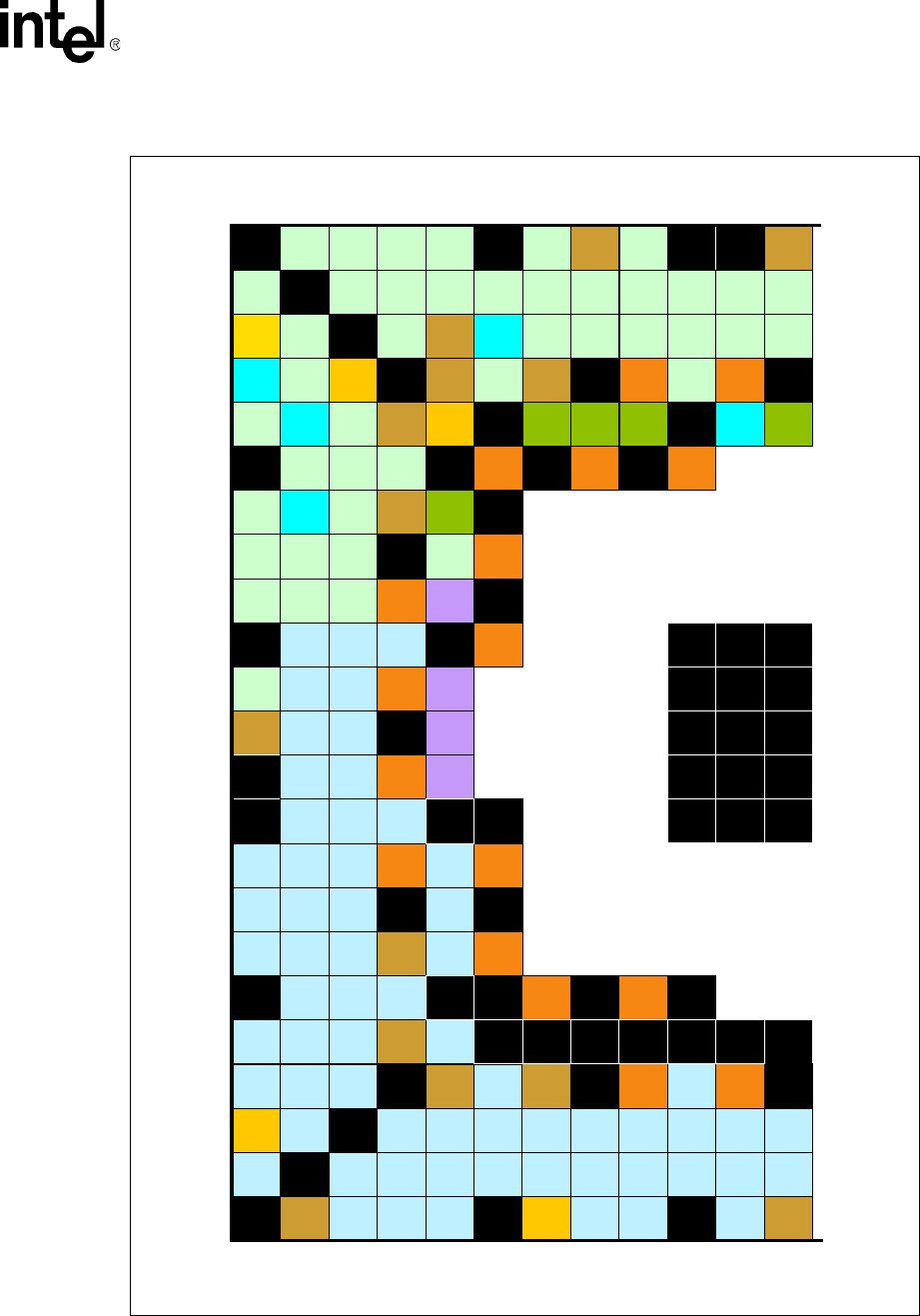

31154 133 MHz PCI Bridge Design Guide Design Guide 15

Package Information

Figure 3. Intel

®

31154 133 MHz PCI Bridge Ball Map—Top View, Left Side

B2240-01

A

1 2 3 4 5 6 7 8 9 10 11 12

1 2 3 4 5 6 7 8 9 10 11 12

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

A

1 2 3 4 5 6 7 8 9 10 11 12

1 2 3 4 5 6 7 8 9 10 11 12

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

VSSVCCP VCC VCC

VSSVSS

VSS

VSS

VSSVCCP VSS VSS VSS VSS

VSS VSS

VSS VSS

VCCP VSS VSS

VSS

VSS

P_

ACK64#

P_

AD56

P_

AD43

P_

AD38

P_

AD45

P_

AD42

P_

AD36

P_

AD41

HS_

SM

P_

AD44

P_

AD46

S_CLK

OEN1

S_CLK

OEN0

S_

AD34

S_

AD33

S_

AD36

S_

AD35

S_

AD32

S_

AD37

S_

AD49

S_

AD48

S_

GNT7#

S_

AD42

S_

AD53

S_

AD52

S_

AD55

S_MAX

100

S_

AD54

S_

GNT6#

S_

AD44

S_

REQ2#

S_CLK

STABLE

S_

AD46

S_

AD57

S_

CBE7#

S_

GNT2#

S_

REQ1#

S_

GNT1#

S_

REQ4#

S_

CBE6#

S_

GNT4#

S_

GNT3#

S_

REQ5#

S_

GNT5#

S_

AD02

S_

AD03

S_

CBE4#

S_

AD58

S_

AD59

S_

AD61

S_

AD60

S_

AD62

S_

AD63

S_

AD01

S_

CBE0#

S_

AD04

S_

AD06

S_

AD00

S_

PAR64

S_

CBE5#

S_

ACK64#

S_

AD56

S_

REQ6#

S_VIO

S_

AD51

S_

AD50

S_

REQ7#

S_

AD47

S_

AD45

S_

AD43

SR_

CLK

SR_CS

S_

AD39

S_

AD38

SR_DO

HS_

LED_

OUT

S_TRI

STATE

HS_

LSTAT

HS_

FREQ0

HS_

ENUM#

SCAN_

EN

S_CLK

OEN2

P_

AD54

P_

AD48

P_

AD47

P_

AD51

P_

AD62

P_

AD53

P_

PERR#

P_

AD58

P_

AD61

P_

CBE5#

P_

REQ64#

P_

STOP#

S_CLK

OEN3

P_

SERR#

P_

AD49

P_

AD50

P_

AD52

P_

AD35

P_

AD39

P_

AD40

P_

AD33

P_

AD32

P_

AD34

P_

AD37

P_

M66EN

P_

AD55

P_

AD57

P_

AD59

P_

AD63

P_

CBE6#

P_

AD60

P_

CBE4#

P_

CBE7#

P_

PAR64

VSS

VSS

VSS VCCP

VCCP VSS VSS VCCP

VCCP VSS

VSS

VSS VCC VCC

VCC

VCC

VCC

VCC

S_

AD41

S_

AD40

SR_DIVCC

VCC VCC

VCC

VCC

NC

VCC

VCC

VCCP VSS

VSS

VSS

VSS

VSS

VCCP VSS

VSS

QE

VSS VSS VSS

VSS VSS VSS

VSS VSS VSS

VSS VSS VSS

VSS

VCCP

VSS

VSS

VSS VSS VSS VCCP

VSS

VCCP

VSSVSS

VCCP VCC VCCVSS

VSS

VSS

VSS

VSS VSS

VSSVCCP R_REF VSS

TMODE

2

CRS

TEN

S_

REQ3#