34 Intel

®

31154 133 MHz PCI Bridge Design Guide Design Guide

PCI/PCI-X Interface

Table 10 describes the bus mode and frequency initialization pattern that the 31154 signals on its

secondary bus when coming out of S_RST#, after having evaluated the above information.

5.6.3 Primary-to-Secondary Frequency Limits

When operating in PCI 33 MHz mode, the bridge bypasses the PLL to allow the full range of

0–33 MHz operations defined in the PCI specifications.

However, the PLL is used to generate the secondary clock outputs when the secondary side is

operating at a frequency greater than 33 MHz (PCI-66 MHz or PCI-X). The primary clock input

must operate above 25 MHz to ensure that the secondary frequencies are within the ranges defined

in the PCI specifications.

When both the primary and secondary sides are operating in PCI-33 MHz mode, then the

secondary clock equals the primary clock in frequency.

An external clock source can be used on the secondary interface to remove any dependencies on

the primary clock input.

§ §

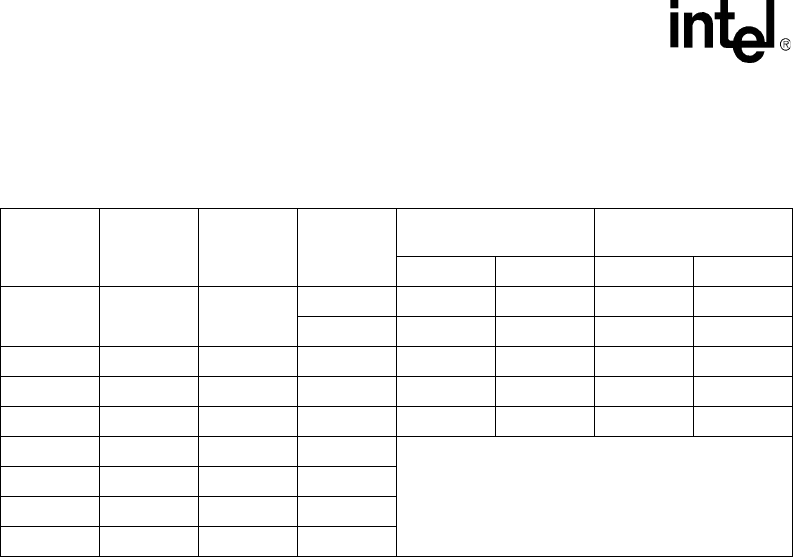

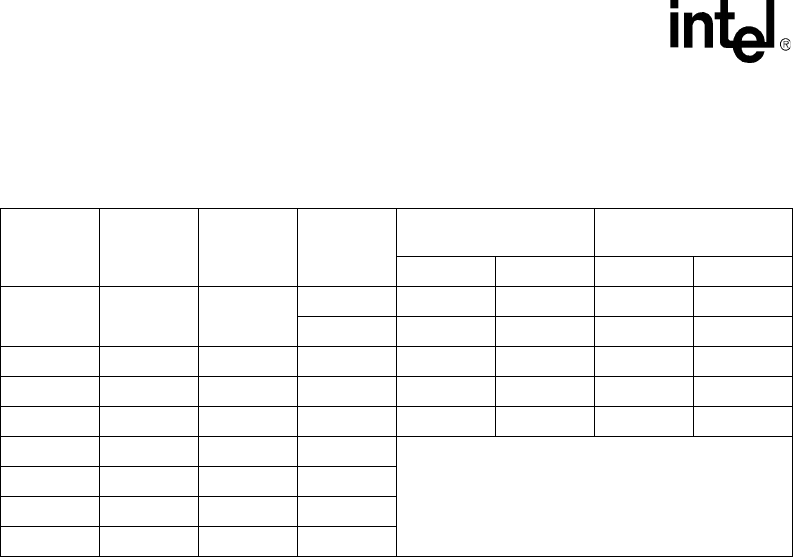

Table 10. PCI-X Initialization Pattern

DEVSEL# STOP# TRDY# Mode

Clock Period

(Ns)

Clock Frequency

(MHz)

Max. Min. Min. Max.

Deasserted Deasserted Deasserted

PCI 33 62.5

1

30 62.5

1

33

PCI 66 30 15 33 66

Deasserted Deasserted Asserted PCI-X 20 15 50 66

Deasserted Asserted Deasserted PCI-X 15 10 66 100

Deasserted Asserted Asserted PCI-X 10 7.5 100 133

Asserted Deasserted Deasserted PCI-X

Reserved

Asserted Deasserted Asserted PCI-X

Asserted Asserted Deasserted PCI-X

Asserted Asserted Asserted PCI-X

NOTE:

1. When the internal PLLs are operational, the minimum input frequency is 16 MHz. See Section 5.6.3,

“Primary-to-Secondary Frequency Limits” on page 34 for more information.