Intel

®

31154 133 MHz PCI Bridge Design Guide Design Guide 47

PCI-X Layout Guidelines

7.2.2 Dual-Slot at 100 MHz

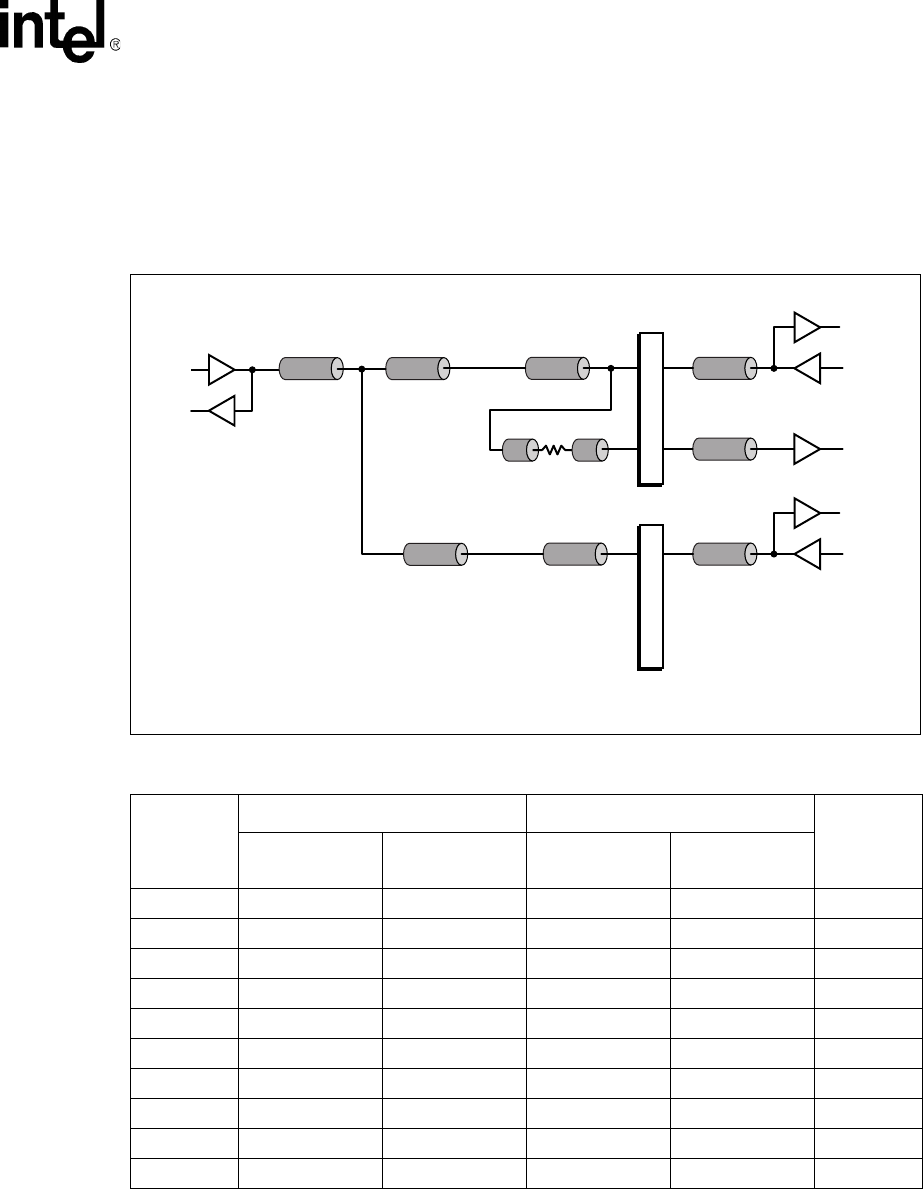

Figure 11 shows one of the secondary bridge PCI AD lines branching into two segments with each

going through slot connectors to a buffer on an add-in card. Table 16 shows the corresponding

wiring lengths to use as a reference. This two-slot design uses a balanced-star topology.

Figure 11. Dual-Slot Configuration

Table 16. Wiring Lengths for 100 MHz Dual-Slot

Segment

Lower AD Bus Upper AD Bus

Units

Minimum

Length

Maximum

Length

Minimum

Length

Maximum

Length

W1 3.5 6 3.5 6 inches

W21 2.0 4.5 1.0 3.5 inches

W11+W12 0.5 0.5 0.5 0.5 inches

W13 0.75 1.5 1.75 2.75 inches

W14 0.1 0.1 N/A N/A inches

W15 0.6 0.6 N/A N/A inches

W16 1.125 1.125 N/A N/A inches

W21 2.0 4.5 1.0 3.5 inches

W22 0.5 0.5 0.5 0.5 inches

WW23 0.75 1.5 1.75 2.75 inches

B3059-01

W1 W11 W12

W14 W15 W16

W13

I/O Buffer

PCI Agent 1

PCI Agent 2

PCI Connector

W21 W22 W23

PCI Connector

Slot 1

Slot 2