106 Intel

®

41210 Serial to Parallel PCI Bridge Developer’s Manual

Register Description

12.2.53 Offset 108h: ERRUNC_MSK—PCI Express*

Uncorrectable Error Mask

This register controls the reporting of individual uncorrectable errors by device to the host bridge

via a PCI Express* error message. This register also controls the logging of the header. Refer to the

PCI Express* specifications for details of how the mask bits function. A masked error (respective

bit set in the mask register) is not reported to the host bridge by the 41210, nor is the header logged

(status bits unaffected by the mask bit). There is a mask bit per bit of the Uncorrectable Error Status

Register (“Offset 104h: ERRUNC_STS—PCI Express* Uncorrectable Error Status Register” on

page 105).

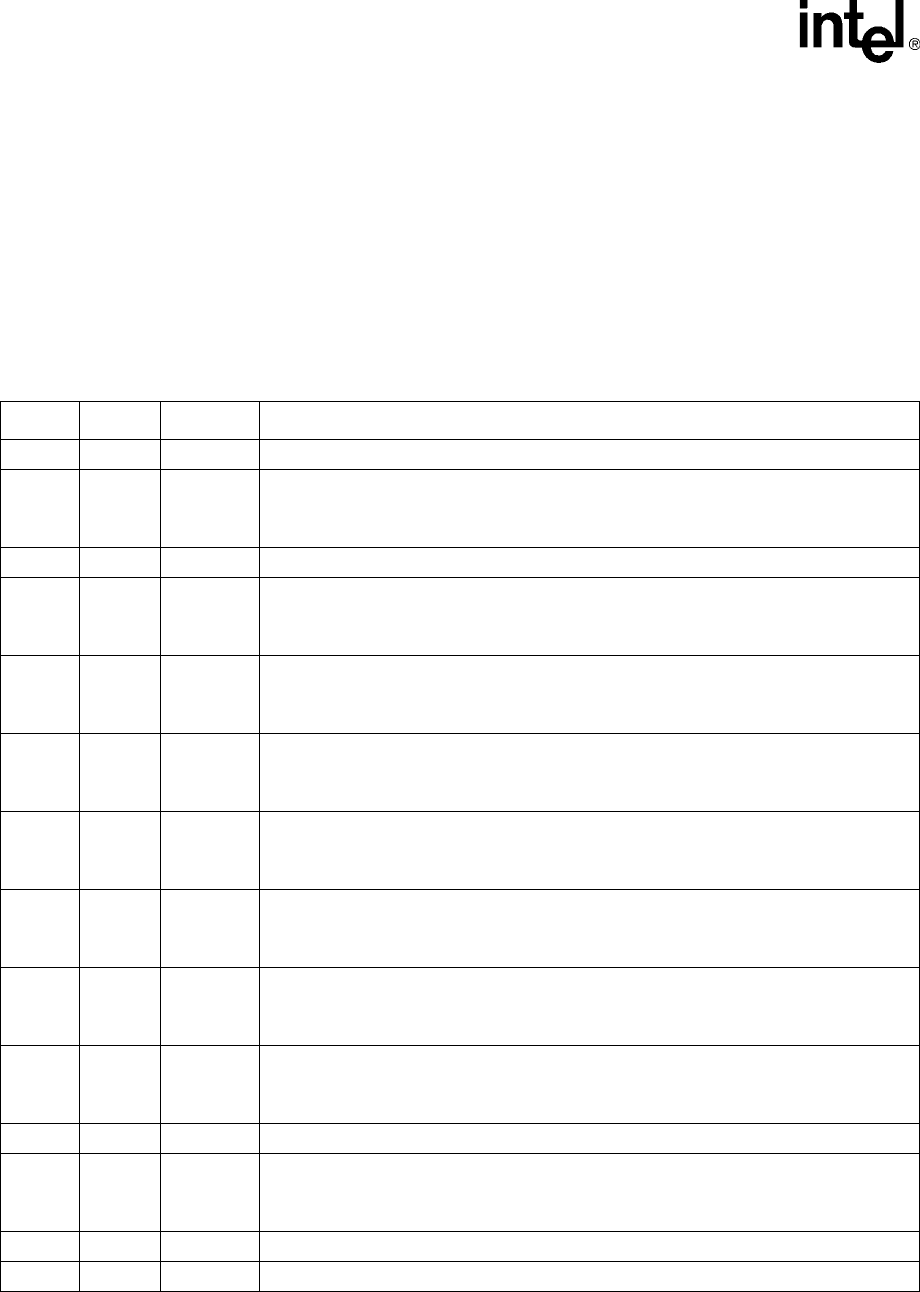

Table 87. Offset 108h: ERRUNC_MSK—PCI Express* Uncorrectable Error Mask

Bits Type Reset Description

31:21 RsvdP 000h Preserved

20 RWCS 0b

Unsupported Request Error Status Error Mask:

0 = Not masked

1 = Masked

19 RO 0b

ECRC Check Error Mask: Not supported

18 RWCS 0b

Malformed TLP Error Mask:

0 = Not masked

1 = Masked

17 RWCS 0b

Receiver Overflow Error Mask:

0 = Not masked

1 = Masked

16 RWCS 0b

Unexpected Completion Error Mask:

0 = Not masked

1 = Masked

15 RWCS 0b

Completer Abort Error Mask:

0 = Not masked

1 = Masked

14 RWCS 0b

Completion Time Out Error Mask:

0 = Not masked

1 = Masked

13 RWCS 0b

Flow Control Protocol Error Status Error Mask:

0 = Not masked

1 = Masked

12 RWCS 0b

Poisoned TLP Received Error Mask:

0 = Not masked

1 = Masked

11:5 RsvdP 00h Preserved

4RWCS 0b

Data Link Protocol Error Mask:

0 = Not masked

1 = Masked

3:1 RsvdP 000b Preserved

0RO 0b

Training Error Mask: Not supported