Intel

®

41210 Serial to Parallel PCI Bridge Developer’s Manual 117

Register Description

12.2.63 Offset 13C–14Bh: PCIXHDR_LOG—Uncorrectable

PCI-X Error Transaction Header Log

This register is the transaction header log for PCI errors. The log in this register corresponds to one

of the status bits set in the PCI-X uncorrectable status register. As soon as an error is logged in this

register, it remains locked for further error logging until the software clears the status bit that

caused the header log (in other words, the error pointer is re-armed to log again).

12.2.64 Offset 16Ah: ARB_CNTRL—Internal Arbiter Control

Register

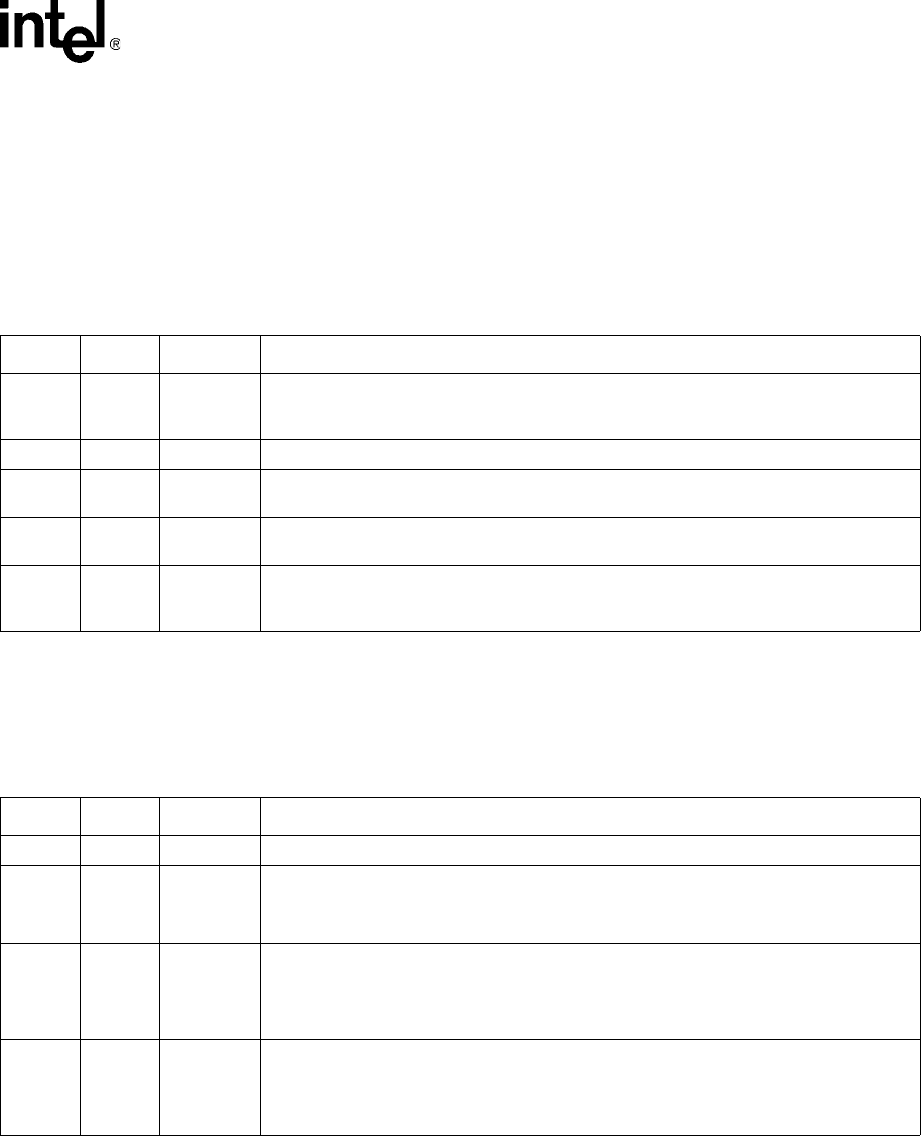

Table 97. Offset 13C–14Bh: PCIXHDR_LOG—Uncorrectable PCI-X Header Log

Bits Type Reset Description

127:64 ROS 0

Address: These bits capture the 64-bit address of the transaction in which an error was

detected. In case of a 32-bit address, the upper address bits are all 0s. The address is

logged on all error conditions.

63:44 ROS 0 Reserved

43:40 ROS 0000b

DAC Bus Command: This field captures the value of C/BE[3:0] during the second address

phase of a DAC transaction.

39:36 ROS 0000b

Bus Command: This field captures the value of C/BE[3:0] during the first address phase of

the transaction.

35:0 ROS 0

Attribute: This field carries the attribute of the transaction. The field is arranged as

<CBE[3:0]#:AD[31:0]> during the attribute phase of the transaction. When the bus is in PCI

mode, this register is all 0s.

Table 98. Offset 16Ah: ARB_CNTRL—Internal Arbiter Control Register

Bits Type Reset Description

15:9 RsvdP 0 Preserved

8RW 0b

Bus Parking Control: This bit controls the bus-parking behavior of the internal arbiter:

0 = The bus is parked on the last PCI agent using the bus.

1 = The bus is always parked on the Intel

®

41210 Serial to Parallel PCI Bridge.

7RW 1b

Bridge Priority Ring Allocation: This bit indicates the priority ring allocation for the 41210

bridge requests:

0 = The 41210 is in the low-priority ring.

1 = The 41210 is in the high-priority ring.

6:0 RW 7Fh

PCI Master Priority Ring Allocation: Bit[0] corresponds to REQ#[0], bit[1] corresponds to

REQ#[1], and so on:

0 = The corresponding master is in the low-priority ring of the internal arbiter.

1 = The corresponding master is in the high-priority ring of the internal arbiter.