Intel

®

41210 Serial to Parallel PCI Bridge Developer’s Manual 109

Register Description

12.2.56 Offset 114h: ERRCOR_MSK—PCI Express*

Correctable Error Mask

This register controls the reporting of individual correctable errors via ERR_COR message. A

masked error (respective bit set in mask register) is not reported to the host bridge by the 41210.

There is a mask bit corresponding to every bit in the Correctable Error Status Register (Offset

110h: ERRCOR_STS—PCI Express* Correctable Error Status).

12.2.57 Offset 118h: ADVERR_CTL—Advanced Error Control

and Capability Register

This register gives the status and control for ECRC checks and also the pointer to the first

uncorrectable error that happened.

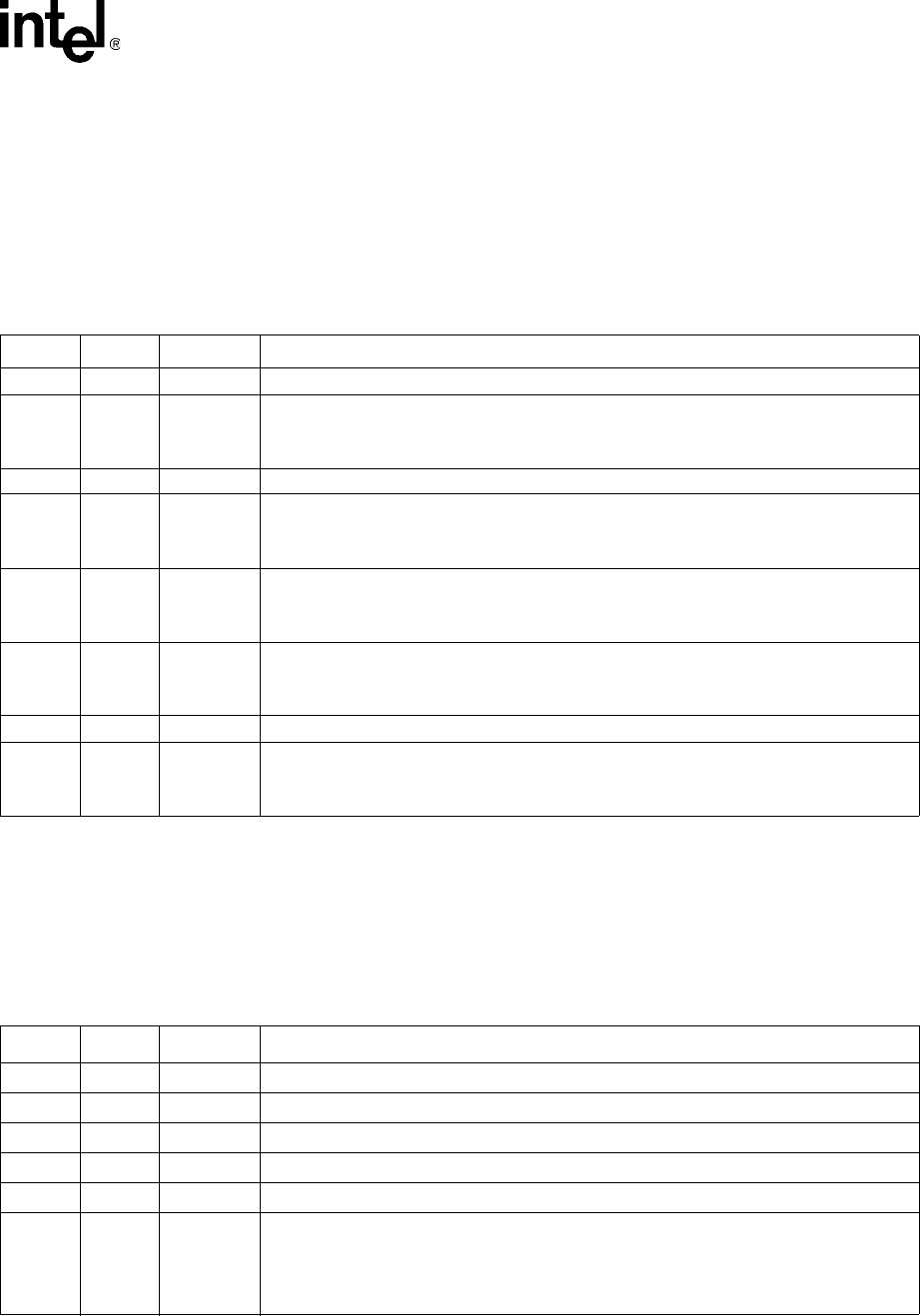

Table 90. Offset 114h: ERRCOR_MSK—PCI Express* Correctable Error Mask

Bits Type Reset Description

31:13 RsvdP 0 Preserved

12 RWS 0b

Replay Timer Time-out Mask:

0 = Not masked

1 = Masked

11:9 RsvdP 000b Preserved

8RWS 0b

Replay Number Rollover Mask:

0 = Not masked

1 = Masked

7RWS 0b

Bad DLLP Mask:

0 = Not masked

1 = Masked

6RWS 0b

Bad TLP Mask:

0 = Not masked

1 = Masked

5:1 RsvdP 0 0000b Preserved

0RWS 0b

Receiver Error Mask:

0 = Not masked

1 = Masked

Table 91. Offset 118h: ADVERR_CTL—Advanced Error Control and Capability Register

Bits Type Reset Description

31:9 RsvdP 0 Preserved

8RO 0b

ECRC Check Enable: Not supported—hard-wired to 0

7RO 0b

ECRC Check Capable: Not supported—hard-wired to 0

6RO 0b

ECRC Generation Enable: Not supported—hard-wired to 0

5RO 0b

ECRC Generation Capable: Not supported—hard-wired to 0

4:0 ROS 0 0000b

The First Error Pointer: This field identifies the bit position of the first error reported in the

Uncorrectable Error Status Register (“Offset 104h: ERRUNC_STS—PCI Express*

Uncorrectable Error Status Register” on page 105). This register re-arms itself (which does

not change its current value) as soon as the error status bit indicated by the pointer is

cleared by the software by writing a 1 to that status bit.