92 Intel

®

41210 Serial to Parallel PCI Bridge Developer’s Manual

Register Description

12.2.26 Offset 46h: EXP_CAP—PCI Express* Capability

This register stores the version number of the capability item and other base information contained

in the capability structure.

12.2.27 Offset 48h: EXP_DCAP—PCI Express* Device Capabilities

Register

This register stores information on the PCI Express* link capabilities.

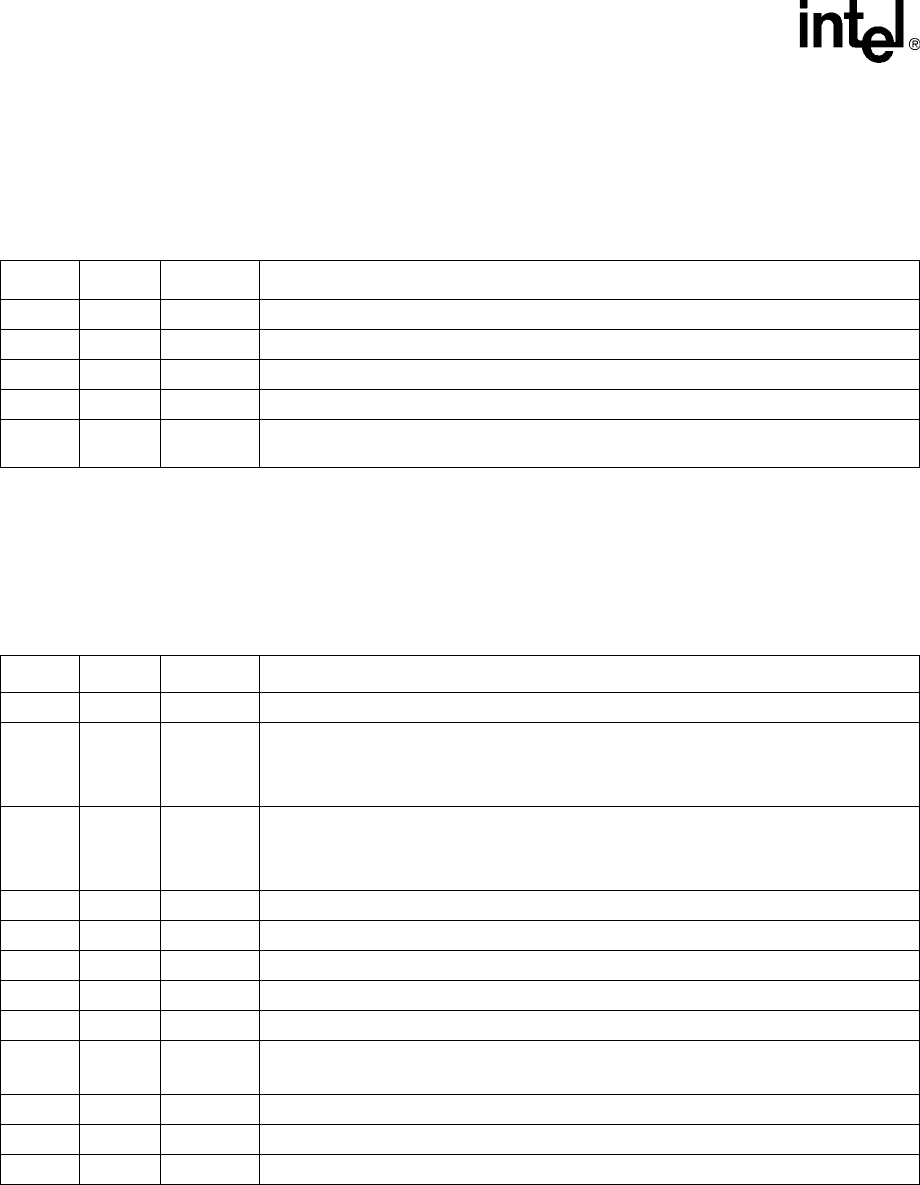

Table 60. Offset 46h: EXP_CAP—PCI Express* Capability

Bits Type Default Description

15:14 RsvdP 00b Preserved

13:9 RO 0 0000b

Interrupt Message Number: Not relevant for the Intel

®

41210 Serial to Parallel PCI Bridge

8RO 0b

Slot Implemented: Not relevant for the 41210

7:4 RO 7h

Device/Port Type: These bits indicate that the 41210 is a PCI Express* end-point device.

3:0 RO 1h

Version Number: These bits indicate the version number of the PCI Express* capability

structure.

Table 61. Offset 48h: EXP_DCAP—PCI Express* Device Capabilities Register

Bits Type Default Description

31:28 RsvdP 0h Preserved

27:26 RO 00b

Captured Slot Power Limit Scale: In combination with the Slot Power Limit value

(bits[25:18], this field specifies the upper limit of the power supplied by slot. The power limit

(in Watts) is calculated by multiplying the value in this field by the value in the Slot Power

Limit Value field. This value is set by the Set_Slot_Power_Limit message.

25:18 RO 00h

Captured Slot Power Limit Value: In combination with the Slot Power Limit Scale value

(bits[27:26]), this field specifies the upper limit of the power supplied by slot. The power limit

(in Watts) is calculated by multiplying the value in this field by the value in the Slot Power

Limit Scale field. This value is set by the Set_Slot_Power_Limit message.

17:15 RsvdP 000b Preserved

14 RO 0b

Power Indicator Present: Not supported

13 RO 0b

Attention Indicator Present: Not supported

12 RO 0b

Attention Button Present: Not supported

11:9 RO 000b

Endpoint L1 Acceptable Latency: L1 ASPM is not supported.

8:6 RO 000b

Endpoint L0s Acceptable Latency: The least latency possible out of L0s is supported.

NOTE: L0s ASPM is not supported in the 41210 Bridge.

5RO 0b

Extended Tag Field Supported: Only a 5-bit tag is supported.

4:3 RO 00b

Phantom Functions Supported: Not supported

2:0 RO 001b

Supported Max Payload sizes: 256-byte packets are the maximum supported.