112 Intel

®

41210 Serial to Parallel PCI Bridge Developer’s Manual

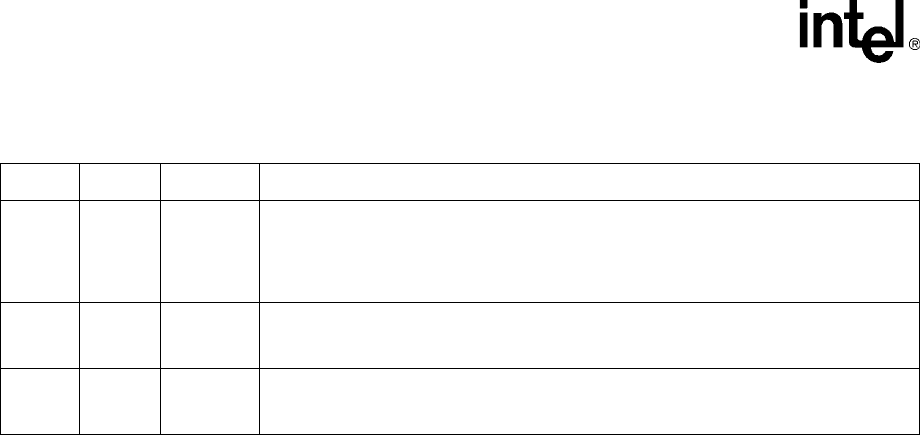

Register Description

2RWCS 0b

PCI-X Detected Target Abort (optional in specification): The 41210 sets this bit when it

is the master of a request transaction on the PCI bus and it receives a target abort. The

41210 logs the header for that transaction. This bit is also set when the bridge receives a

PCI-X Split Completion Message with Target Abort Status. The header log under this

condition is the command, address, and attribute portion of the Split Completion Message.

1RWCS 0b

PCI-X Detected Split Completion Master Abort: The 41210 sets this bit when a split

completion sent by the 41210 on the PCI-X bus master-aborts. The 41210 logs the header

of the split completion.

0RWCS 0b

PCI-X Detected Split Completion Target Abort (optional in specification): The 41210

sets this bit when a split completion sent by the 41210 on the PCI-X bus target-aborts. The

41210 logs the header.

Table 93. Offset 12Ch: PCIXERRUNC_STS—Uncorrectable PCI-X Status Register

(Sheet 2 of 2)

Bits Type Reset Description