Intel

®

41210 Serial to Parallel PCI Bridge Developer’s Manual 73

Register Description

Register Description 12

This chapter describes the registers of the Intel

®

41210 Serial to Parallel PCI Bridge.

12.1 Register Nomenclature and Access Attributes

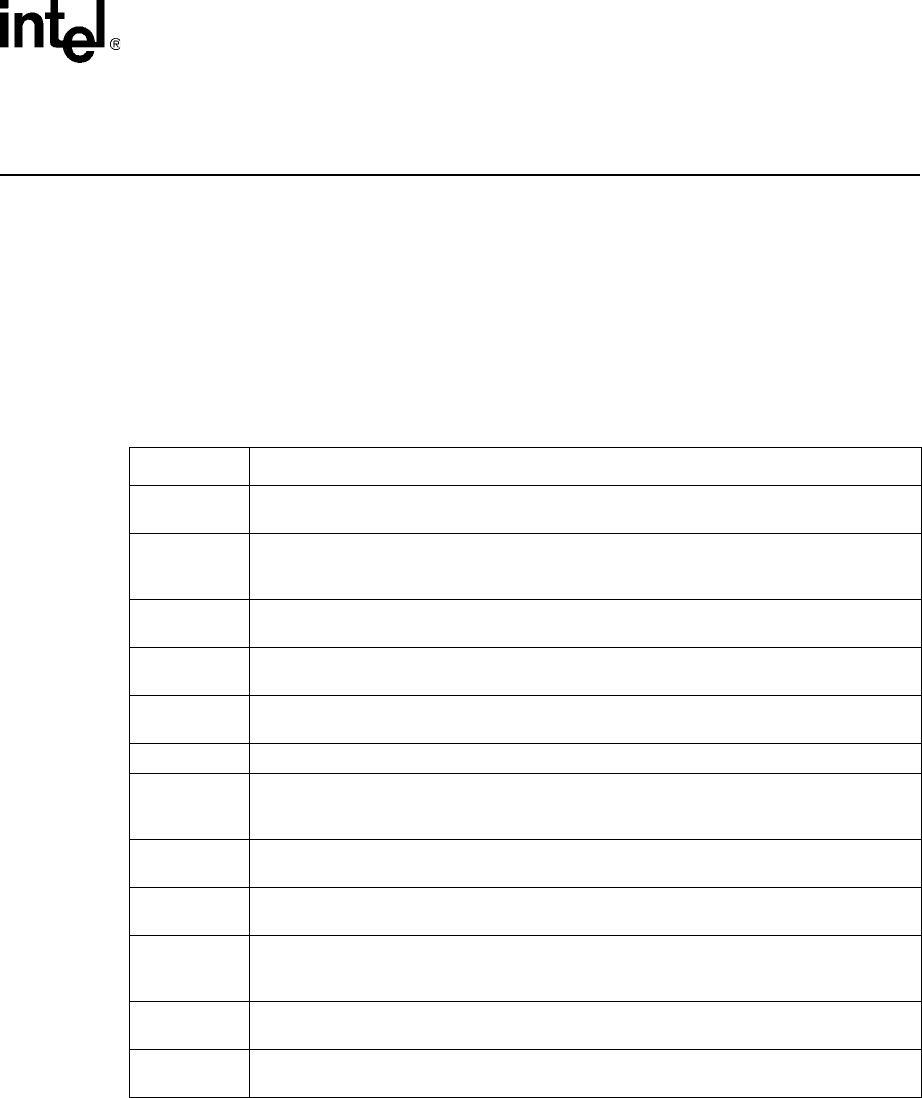

Table 32 describes the nomenclature used for describing bit attributes throughout this chapter.

Note: Software must not attempt to write to the registers that are marked “reserved”. Writing to these

registers yields undetermined results. Reads of these registers can yield either value. Note that the

behavior of individual register bits that are marked “reserved” is in accordance with the attribute

definition for that bit.

Table 32. Bit Attribute Definitions

Mnemonic Attribute

RO

Read-Only: This bit cannot be altered by software. This bit can be hard-wired to return a

fixed value at all times, or it can be set by hardware on an event.

RsvdP

Reserved and Preserved: These bits are reserved for future RW implementations; software

must preserve the value read for writes to bits. The Intel

®

41210 Serial to Parallel PCI Bridge

hardware implements these bits as read-only 0s.

RsvdZ

Reserved and Zero: These bits are reserved for future RWC implementations; software must

use 0 for writes to bits. The 41210 hardware implements these bits as read-only 0s.

ROS

Read-Only Sticky: These bits are read-only and cannot be altered by software. The bits are

not cleared by reset and can be reset only with the

PERST# reset condition.

RZSet

Read Zero to Set: Reading this bit when the current value of the bit is 0 causes the bit to flip

to a 1. Software must write a 1 to clear this bit. Writing a 0 has no effect.

RW

Read-Write: Software can do a full read and write of this bit.

RW1Set

Read and Write One to Set: Software must write a 1 to set this bit. Writing a 0 has no effect

on this bit. Software can clear this bit through a separate RWC bit, or it can be reset by

hardware.

RWS

Read-Write and Sticky: Software can read and write this bit. The bit can be reset only by a

PERST# reset.

RWC

Read and Write One to Clear: When this bit is set, software must write a 1 to this bit to clear

it. Writing a 0 has no effect.

RWCS

Read and Write One to Clear and Sticky through reset: When this bit is set, software must

write a 1 to this bit to clear it. Writing a 0 has no effect. The bit can be reset only by a

PERST#

reset.

Strap

Strap: This is a read-only register. The power-on default is based on sampling a strap pin at

the rising edge of

PERST#.

WT

Write Transient: This bit is always read as a 0. Writing a 1 to this bit causes other side-

effects that are specific to every WT bit.