Motherboard Layout and Routing Guidelines

2-16

Intel

®

440GX AGPset Design Guide

2.6.2 Signal Quality Measurement

Signal integrity is specified at the processor core, which is not accessible. Intel has found that there

can be substantial miscorrelation between ringback at the edge finger versus the core. The

miscorrelation creates instances where a signal fails to satisfy ringback requirements at the edge

finger, but passes the ringback specification at the core. For this reason, signal integrity is specified

at the core. Ringback guidelines are supplied at the edge finger, as shown in Table 2-6. Any

measurement at the edge finger that violates the guidelines should be simulated to verify that it

meets the specification at the core.

NOTE:

1.

Rin

g

back specifications follow the methodolo

gy

described in

Intel

®

Pentium

II

Processor at 233 MHz, 266

MHz, 300 MHz and 333 MHz

Datasheet.

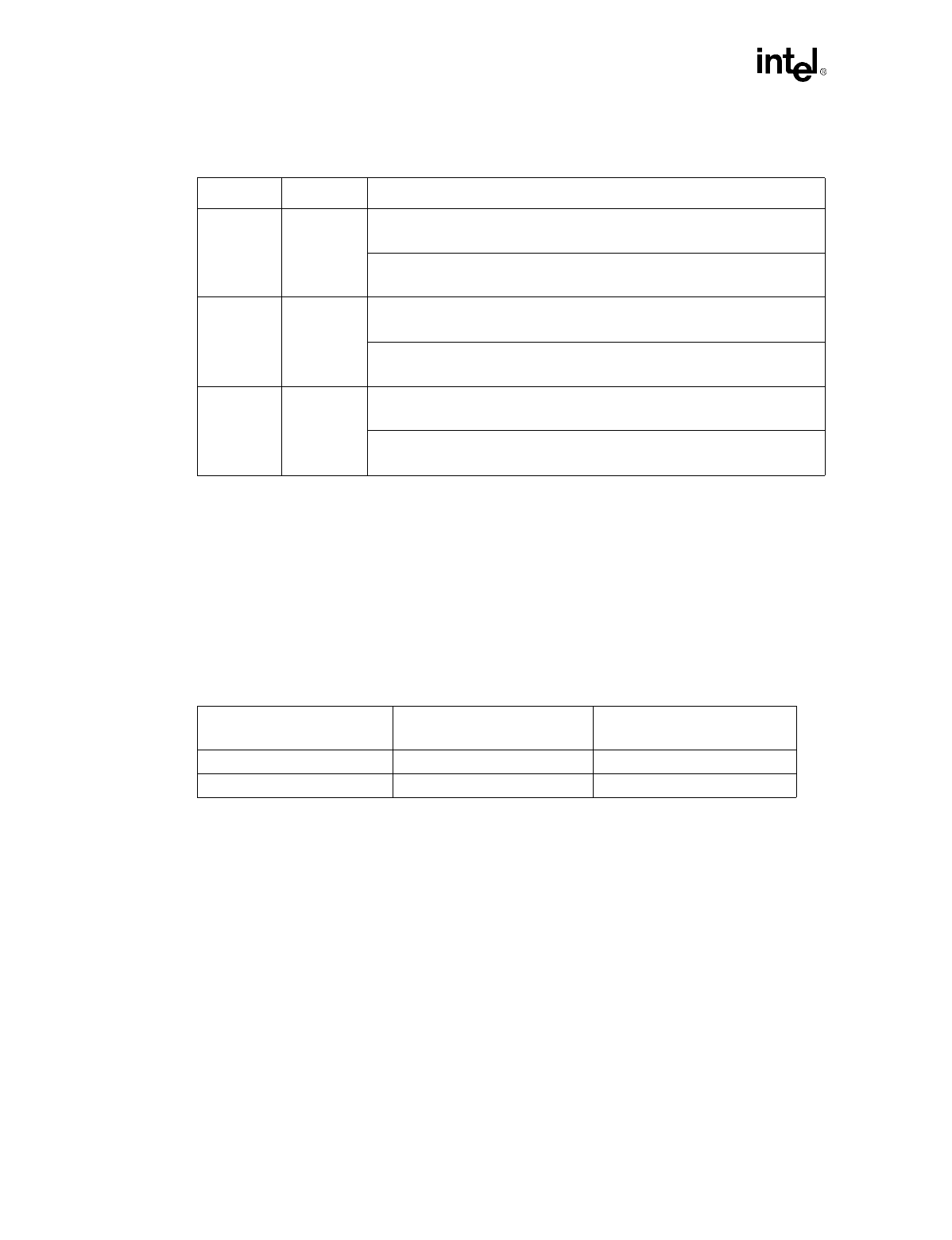

Table 2-5. System Timing Requirements for Validating Setup/Hold Windows

Driver Receiver Equation

Pentium

®

II

processor

AGPset

AGPset

Pentium

®

II

processor

Pentium

®

II

processor

Pentium

®

II

processor

TTTTT

measured hold skew CLK skew PCB clk

≥+ + +

, , ,max

TTTTTTTT

measured cycle su skew CLK skew PCB jit adj clk

≤−− − −−+

,, ,min

TTTTT

measured hold skew CLK skew PCB clk

≥+ + −

, , ,min

TTTTTTTT

measured cycle su skew CLK skew PCB jit adj clk

≤−− − −−−

,, ,max

TTTT

measured hold skew CLK skew PCB

≥+ +

,,

TTTTTTT

measured cycle su skew CLK skew PCB jit adj

≤−− − −−

,,

Table 2-6.

Rin

g

back Guidelines at the Intel

®

Pentium

®

II

Processor Ed

g

e Fin

g

ers

Edge

Guideline @ Processor Edge

Finger

Spec @ Processor Core

Rising 1.29V 1.12V

1

Falling 0.71V 0.88V