Intel

®

440GX AGPset Design Guide

3-12

Design Checklist

•

GTLREFx pins are driven from independent voltage dividers which set the GTLREFx pins to

VTT*2/3 using a 75 ohm and 150 ohm resistor ratio.

•

The 82443GX GTL_REF[B:A] pins should be adequately decoupled.

•

The 82443GX component is a 3.3V component. All pins labeled as VDD should be connected

to VCC

3.3

.

•

VDD_AGP pins have been changed to VDD pins.

•

The VSSA pin has been changed to VSS.

•

The 82443GX REFVCC5 pin can be connected to the same power sequencing circuit used by

the PIIX4E. See the PIIX4E section for further information on sharing this circuit.

•

The 82443GX AGPREF pin is required to be 0.4 of VCC

3.3

, this can be performed by a

voltage divider.

•

The 82443GX GX_PWROK can be connected to the PIIX4E PWROK pin.

•

The 22 ohm series resistors on GCLKOUT and GCLKIN should be placed next to the driver

GCLKOUT.

•

CRESET# is used to control the reset values of A20M#, IGNNE#, and LINT[1:0] and

determine the ratio of core and bus frequencies. This signal is delayed to provide the two

BCLK hold requirement. A 10K ohm pull-up to 3.3V is recommended.

•

TESTIN# should be pulled up to VCC

3.3

with an 8.2K ohm resistor. The internal pull-up may

prove to be sufficient, however the first rev of boards should include the external pull-up to be

safe.

3.5.2 82443GX GTL+ Bus Interface

•

The Intel

®

440GX AGPset does not support the entire Intel

®

Pentium

®

II processor GTL+

bus. For a UP design, on board termination resistors are recommended for the following

signals: HD[63:0]#, A[31:3]#, HREQ[4:0]#, RS[2:0]#, HTRDY#, BREQ[0]#, BNR#, BPRI#,

DBSY#, DEFER#, DRDY#, ADS#, HIT#, HITM#, HLOCK#, CPURST#. The second set of

terminations are provided on the Intel

®

Pentium

®

II processor.

•

The Intel

®

440GX AGPset does not support the entire Intel

®

Pentium

®

II processor GTL+

bus. For a DP design, on board termination resistors are NOT required for the following

signals: HD[63:0]#, A[31:3]#, HREQ[4:0]#, RS[2:0]#, HTRDY#, BREQ[0]#, BNR#, BPRI#,

DBSY#, DEFER#, DRDY#, ADS#, HIT#, HITM#, HLOCK#, CPURST#. The second set of

terminations are provided on the second Intel

®

Pentium

®

II processor or terminator card. An

empty Slot 1 connector is not allowed.

3.5.3 82443GX PCI Interface

•

If boundary scan is not supported on the motherboard: (See the PCI Specification Rev 2.1

Section 4.3.3 for more information)

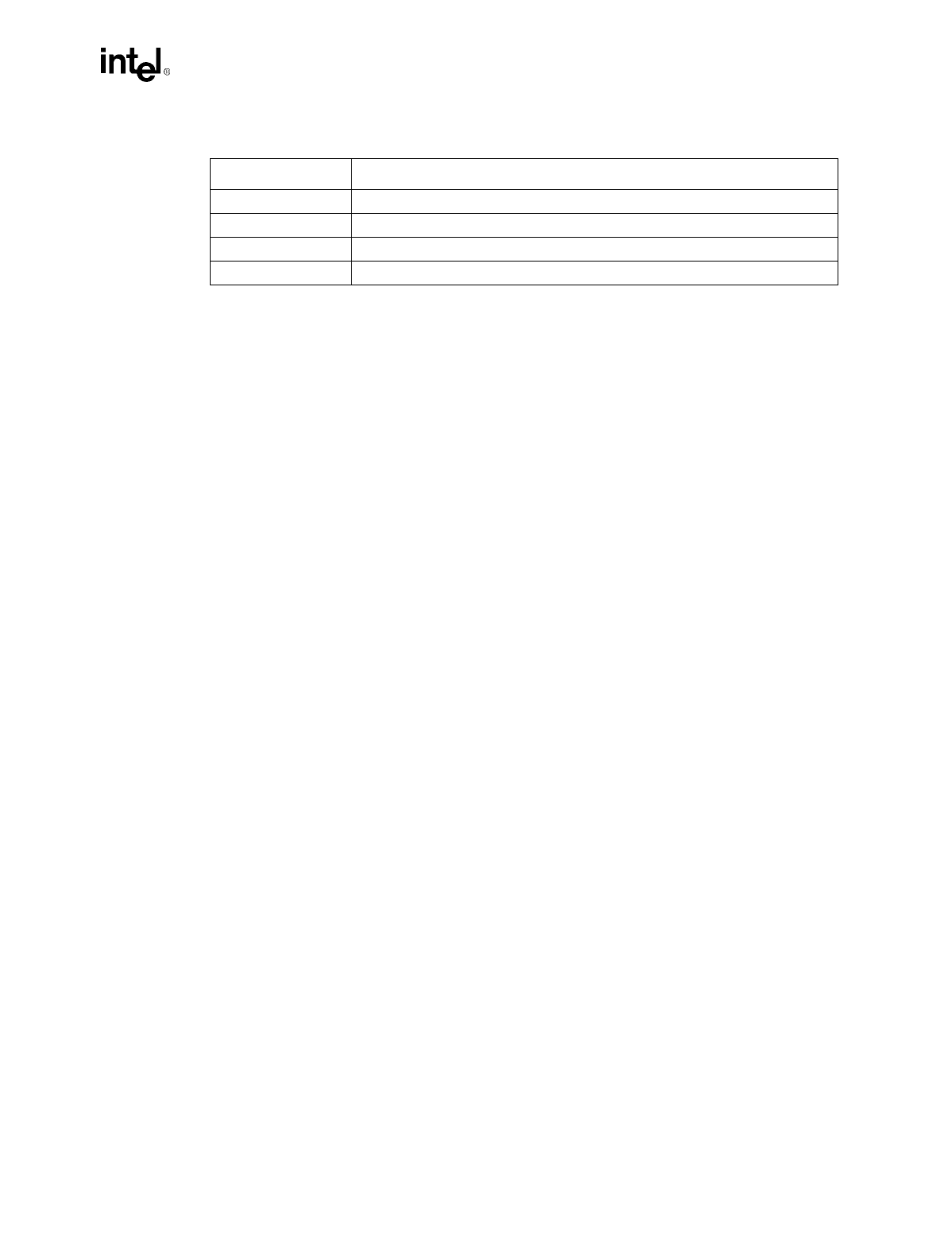

TRDY# 2.7K ohm pull-up to 5V. Connected to PCI bus.

VTTA, VTTB GTL threshold voltage for early clamps.

WE[B:A]# Each connected to up to 2 DIMMs.

WSC#

UP

: Leave as a NC.

DP

: Connected to IOAPIC. No pull-up resistor is needed.

Table 3-4. 82443GX Connectivity (Sheet 3 of 3)

SIGNAL CONNECTION