Motherboard Layout and Routing Guidelines

2-24

Intel

®

440GX AGPset Design Guide

2.9.1.3 Trace Width vs. Trace Spacing

To minimize the crosstalk, a 1:2 trace width vs. trace spacing routing (e.g., 6 mils on 9 mils or 5

mils on 10 mils) should be used for all memory interface signals.

2.9.2 Memory Layout & Routing Guidelines

Layout Guidelines: All signals require careful routing for both min and max trace lengths

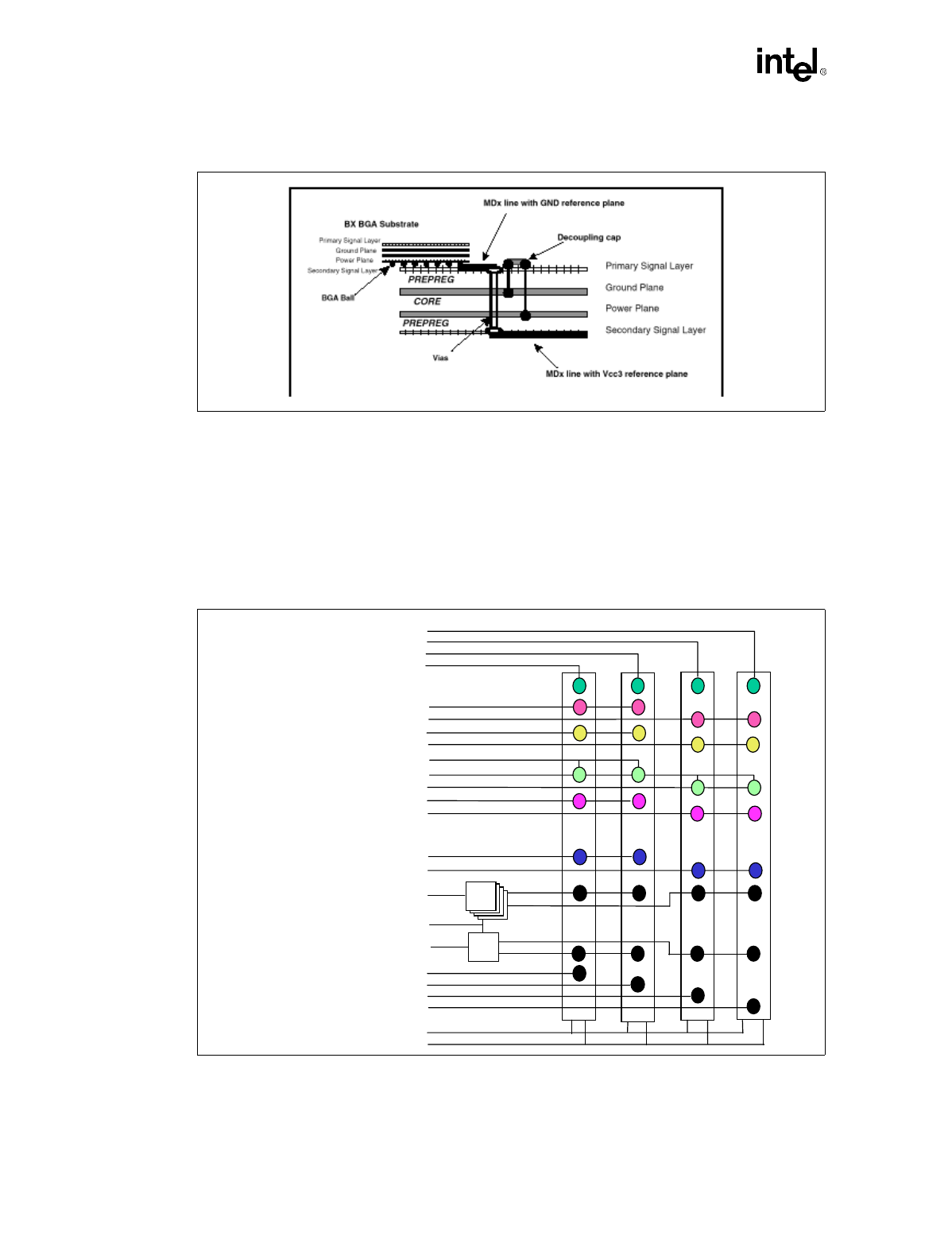

Figure 2-18. Matching the Reference Planes and Adding Decoupling Capacitor

Figure 2-19. 4 DIMMs (Single or Double-Sided)

CS_A[7:6]#,CS_B[7:6]#

CS_A[5:4]#,CS_B[5:4]#

CS_A[3:2]#,CS_B[3:2]#

CS_A[1:0]#,CS_B[1:0]#

SMB_CLK

SMB_DATA

DIMM_CLK[3:0]

DIMM_CLK[7:4]

DIMM_CLK[11:8]

DIMM_CLK[15:12]

SRAS_A#

SRAS_B#

SCAS_A#

SCAS_B#

WE_A#

WE_B#

DQM_B[1,5]

MAA[14:0]

MAB[12, 11, 9:0]#, MAB[14, 13,10]

MECC[7:0]

MD[63:0]

DQM_A[1,5]

DQM_A[7,6,4:2,0]

~ 16212

~ 16212

FENA

Group 0 Group 1