Motherboard Layout and Routing Guidelines

2-30

Intel

®

440GX AGPset Design Guide

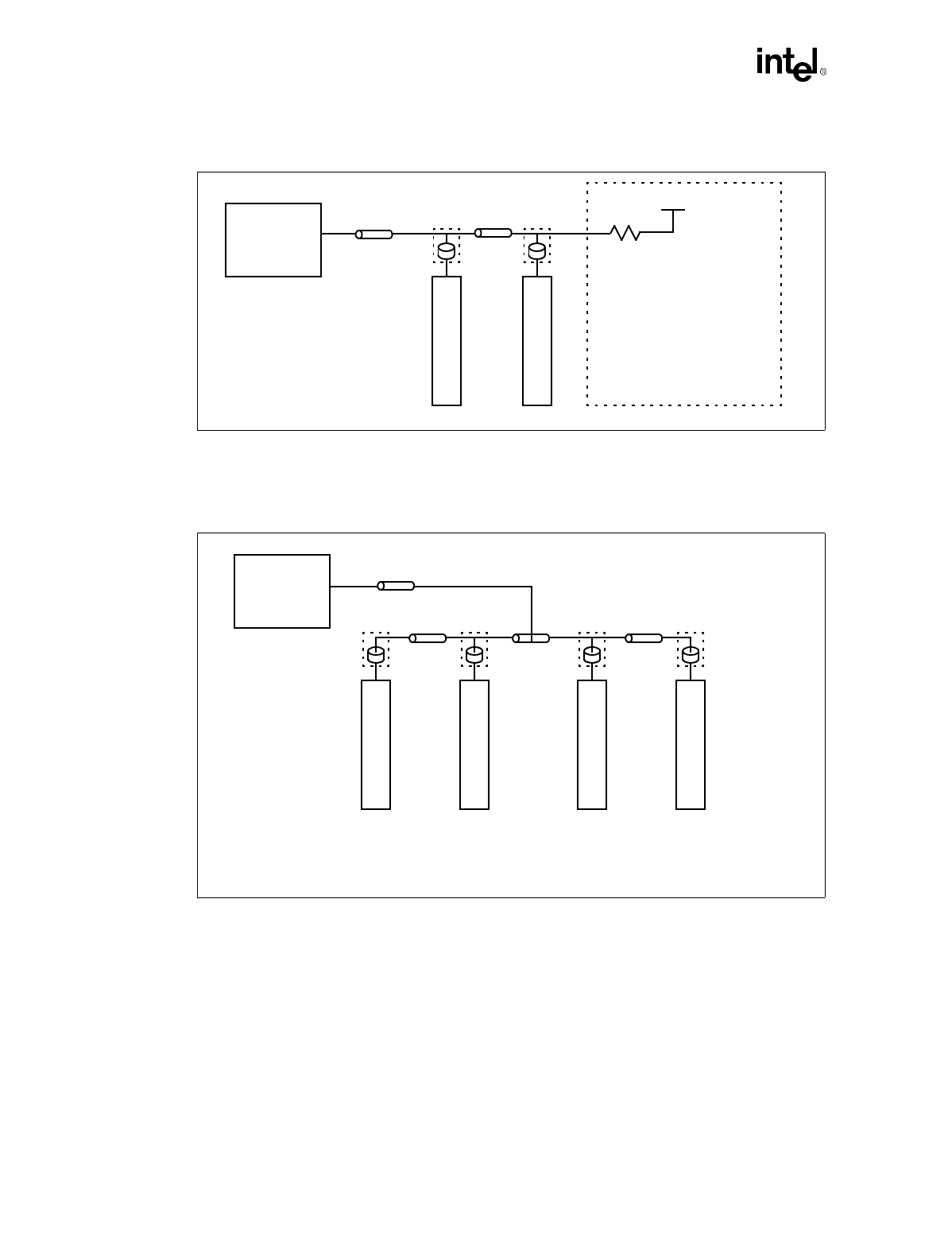

2.9.3 4 DIMM Routing Guidelines [NO FET]

2.9.4 PCI Bus Routing Guidelines

The 82443GX provides a PCI Bus interface that is compliant with the PCI Local Bus Specification.

The implementation is optimized for high-performance data streaming when the 82443GX is

acting as either the target or the initiator on the PCI bus. For more information on the PCI Bus

interface, refer to the Intel

®

440GX AGPset Datasheet.

An Intel

®

440GX AGPset PCI Bus design is basically the same as the Intel

®

440BX AGPset. The

Intel

®

440GX AGPset supports 5 PCI Bus masters (excluding the Intel

®

440GX AGPset and

PIIX4E), by the support of 5 PREQ# and PGNT# lines.

Table 2-25. Motherboard Model: MA_B[12,11,9:0]#, MA_B[14,13,10], 4 DIMMs

Figure 2-27. Motherboard Model—Data (MDxx) Lines, 4 DIMMs (No FET)

82443GX

1.0” - 3.0”

DIMM Module 3

V

CC3

10 K

Ω

Max stub to 10 K

Ω

pullup/pulldown at end

of line:

0.2” - MAB12#

0.5” - MAB[11,9]#

(only applies to straps)

0.4” - 0.6”

DIMM Module 4

82443GX

2” - 3”

0.4”

DIMM Module 1

DIMM Module 2

0.4”

DIMM Module 3

DIMM Module 4

0.2”

0.2”

NOTE:

1. Route using

≤ 6

mil trace and

≥

12 mil spacing. Route on outer layers.

Trace impedance Z = 60–80 ohms.

Trace velocity = 1.6–2.2 ns/ft