Intel

®

440GX AGPset Design Guide

3-27

Design Checklist

(WP# pin not available on 8-Mbit 44-lead PSOP. In this package, treat as if the WP# pin is

internally tied low, effectively eliminating the last row of the table below.)

•

Use either A16 or A17 inversion for both the 2Mbit or 4Mbit to differentiate between recovery

and normal modes.

•

If migrating a BV design to the lower cost B5 device, Application Brief AB-65 “Migrating

SmartVoltage Boot Block Flash Designs to Smart 5 Flash” is available (Order#292194).

NOTES:

1. V

PPLK

is specified at 1.5V(maximum).

2. V

IL

is specified at logic low.

3. V

IH

is specified at logic high.

4. V

HH

is specified at 12V

±

5%.

•

Use SUSA# to drive the flash RP# pin into the deep power-down mode when system is in the

suspend states.

•

(SUSA# Alternative) Use system “POWEROK” or “POWERGOOD” signal to drive flash RP#

to keep device in deep power down during power-up only (write protection). For systems not

needing power saving modes.

•

Connect BYTE# to GND for byte-wide mode operation if x16 device is used.

•

Use a 0.01mf - 0.1mf ceramic capacitor connected between each Vcc and GND, and between

its Vpp and GND. These high frequency, inherently low inductance capacitors should be

placed as close as possible to the package leads.

•

Add information on how BIOSCS# elevates the need for control logic and GPO[x] control on

WE#

•

Add information on ISA load consideration and the reduction of the X-bus drivers/control

Figure 3-7 illustrates the recommended layout for Intel’s flash devices in desktop designs:

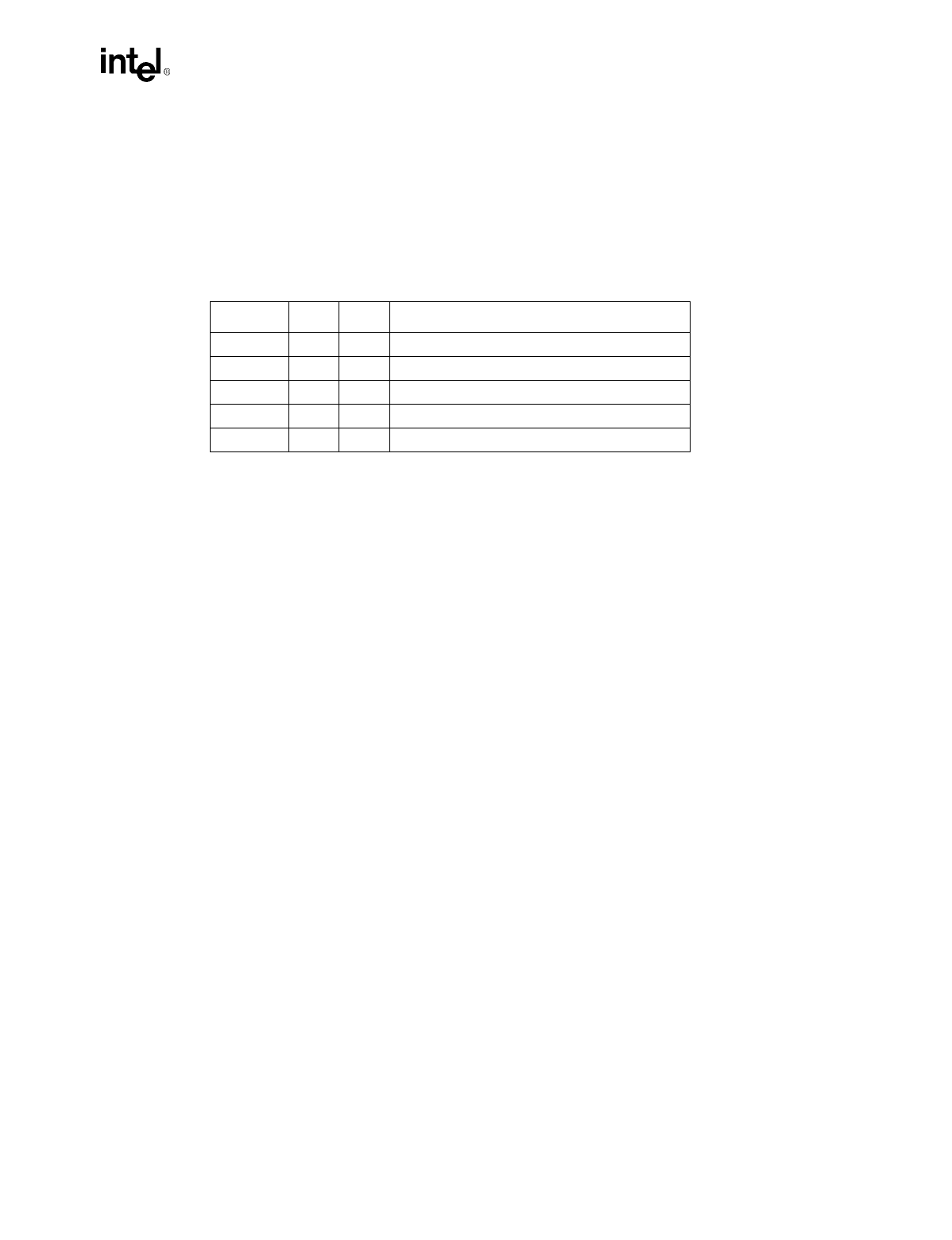

Table 3-13. Flash Vpp Recommendations

VPP RP# WP# Write Protection

VIL X X All Blocks Locked (Programming)

≥

VPPLK VIL X All Blocks Locked (All operations)

≥

VPPLK VHH X All Blocks Unlocked (All operations)

≥

VPPLK VIH VIL Boot Block Locked (Programming)

≥

VPPLK VIH VIH All Blocks Unlocked (All operations)