Intel

®

440GX AGPset Design Guide

3-13

Design Checklist

— TMS (connector pin A3) and TDI (connector pin A4) should be independently bussed and

pulled up with 5K ohm (approximate) resistors.

— TRST# (connector pin A1) and TCK (connector pin B2) should be independently bussed

and pulled down with 5K ohm (approximate) resistors.

— TDO (connector pin B4) should be left open.

3.5.4 82443GX AGP Interface

•

The following will help reduce the AGPREF margin needed when data is being written or read

via the AGP bus interface.

— Use only two 1% resistors for the AGPREF voltage divider on the 82443GX boards. This

will limit the AGPREF margin needed to 100mV below 40% of Vcc. If 5% resistors are

used, the AGPREF margin needed would be 160mV.

— Have “at least” 2x spacing around Strobe A and B to decrease crosstalk inductive coupling

from adjacent GAD signals. This could reduce crosstalk by as much as 100-300 mV.

•

The AGP interface is designed for a 3.3V operating environment, and both the master and

target AGP compliant devices must be driven by the same supply line.

•

No external termination for signal quality is required by the AGP spec., but can be added to

improve signal integrity provided the timing constraints are still satisfied.

•

AGP interrupts may be shared with PCI interrupts similar to the recommendations in the PCI

2.1 spec. For example, in a system with 3 PCI slots and one AGP slot, interrupts should be

connected such that each of the four INTA# lines hooks to a unique input on the PIIX4E. It is

recommended that the interrupts be staggered. It is also recommended that each PIRQ be

programmed to a different IRQ if possible.

•

It is the requirement of the motherboard designer to properly interface the AGP interrupts to

the PCI bus. In this reference design, the AGP interrupts are pulled up to 3.3V, and a buffer is

used to isolate the 5V environment from the AGP bus.

•

To minimize the impact of any mismatch between the motherboard and the add-in card, a

board impedance of 65 ±15 ohms is strongly recommended.

•

At each component that requires it, AGP_Vref should be generated locally from the AGP

interface Vddq rail.

NOTES:

1. MAB[9]# is connected to internal 50K ohm pull-down resistors. MAB[12:11] are connected to internal 50K

ohm pull-up resistors.

2. Note that strapping signals are not driven by the 82443GX during reset sequence. Proper strapping must be

used to define logical values for these signals. Default values provided by the internal pull-up or pull-down

resistors can be overridden by an external resistor.

3. When AGP is disabled, all AGP signals are tri-stated and isolated. They do not need external pull-up

resistors. The AGP signals are PIPE#, SBA[7:0], RBF#, ST[2:0], GADSTBA, GADSTBB, SBSTB, GFRAME#,

GIRDY#, GTRDY#, GSTOP#, GDEVSEL#, GREQ#, GGNT#, GAD[31:0], FC/BE[3:0]#, GPAR.

4. When AGP is disabled, tie AGP_Vref to ground.

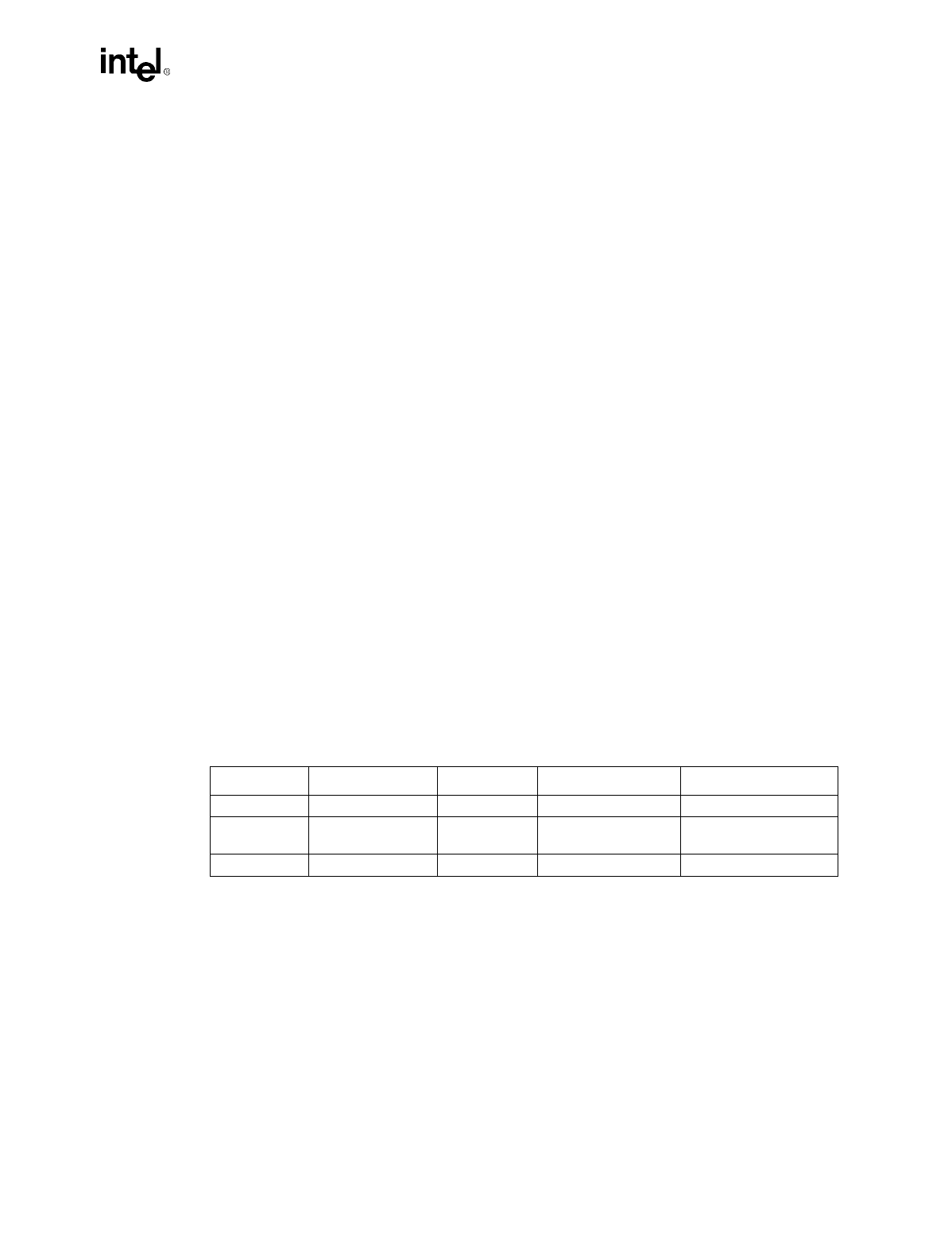

Table 3-5. Strapping Options

Signal Description Register Pulled to ‘0’ Pulled to ‘1’

MAB9# AGP Signals PMCR[1] AGP Enabled (Default) AGP Disabled

MAB11#

In Order Queue

Depth

MGXCFG[2] Non-Pipelined

Maximum Queue Depth

Enabled (Default)

MAB12# Host Frequency NGXCFG[13] Reserved 100MHz (Default)