3 - 5 3 - 5

MELSEC-Q

3 SPECIFICATIONS

REMARK

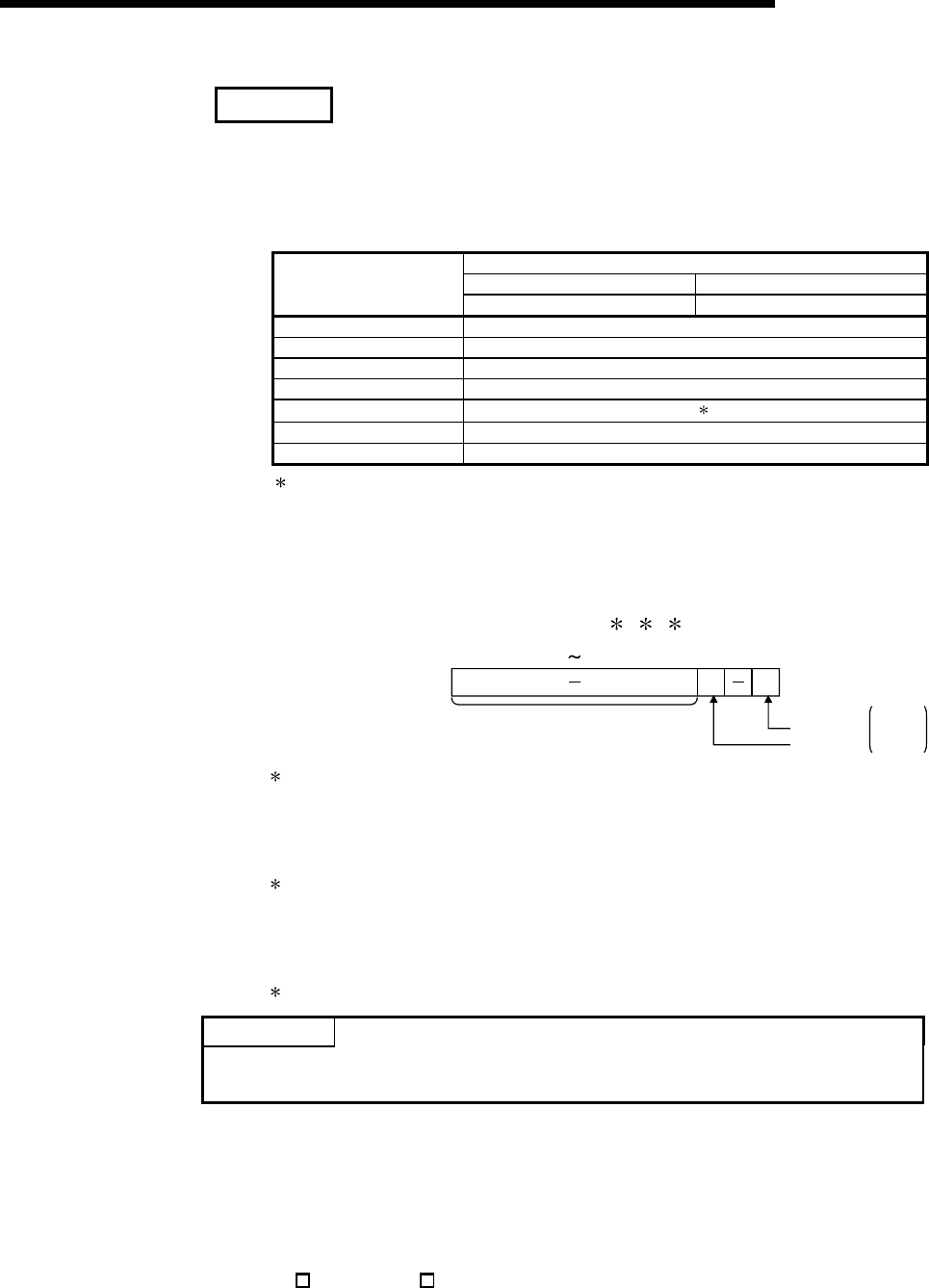

(1) Confirmation of RS-232 control signal status

The control signal status of DTR, DSR, RS, and CD can be confirmed during

data communication by the RS-232 control signal status storage area (address

254

H

, 264

H

) of the GX Configurator-SC or Q series C24 buffer memory.

Buffer memory address

CH1 side CH2 sideBit position

254

H

264

H

b0 RS

b1 DSR

b2 DTR

b3 CD

b4

CS

1

b5 RI

b6 to b15 —

1 System area for QJ71C24 (-R2)

(2) Designation of RS and DTR signal status

When the Q series it turned on or off, the on and off states of the RS and DTR

signals can be designated when the buffer memory of the RS and DTR signal

status designation area (address: 92

H

, 132

H

) for the corresponding bit is turned

on or off by the RS signal or DTR signal.

1

2

3

Buffer memory address 92

H

/132

H

1/0

b15 b3 b2 b1 b0

1/0

System

1:ON

0:OFF

RS

DTR

[Default 0005

H

]

1 The RS signal is controlled by the Q series C24 in the following cases. (Ignore setting

contents.)

• When data is communicated with half-duplex communication

• When communication time and the RS and CS signals are controlled by the modem function

2 The DTR signal is controlled by the Q series C24 in the following cases. (Ignore setting

contents.)

• When the DTR and DSR signals are controlled

• When data is communicated by the modem function

3 After writing in the buffer memory, a lag of 0 to 20 ms occurs until it is reflected in the signal.

POINT

Be sure to control the RS and DTR signals with the Q series C24. Control of the RS

and DTR signals by the user is a prime factor for data communication errors.

3.2.2 RS-232 cable specification

• Use a 15 m (49.21 ft.), or shorter, cable conforming to the RS-232 standard as the

RS-232 cable.

(Recommended cable)

7/0. 127

P HRV-SV… : Designates the number of pairs. (For 13 pairs 7/0.127

13P HRV-SV)

(Oki Electric Cable Co., Ltd)