4 - 14 4 - 14

MELSEC-Q

4 SETTINGS AND PROCEDURES PRIOR TO OPERATION

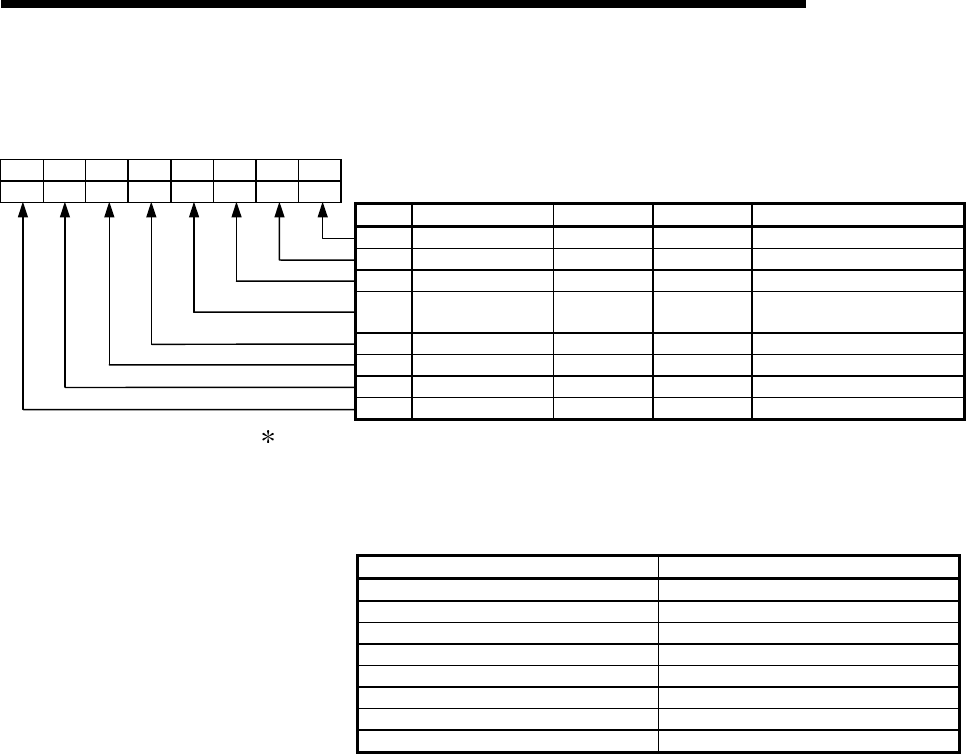

(a) Transmission setting (CH1 side: switch 1 (lower level); CH2 side: switch 3

(lower level))

b7 b6 b5 b4 b3 b2 b1 b0

CH1 side

CH2 side

Bit Description OFF (0) ON (1) Remarks

b0 Operation setting Independent Link Must be set to OFF on CH1

b1 Data bit 7 8 Parity bit is not included

b2 Parity bit NO Yes Vertical parity

b3 Even/odd parity Odd Even

Valid only when parity bit is set to

Yes

b4 Stop bit 1 2 —

b5 Sum check code NO Yes —

b6 Write during RUN Prohibited Allowed —

b7 Setting modifications Prohibited Allowed —

All items listed in the table should be set to OFF for the interfaces for which

"GX Developer connection" is set in the communication protocol setting.

If connecting directly to the GX Developer, it operates with the setting value

on the GX developer. (Refer to the description below.)

Transmission setting Setting description for GX Developer

Operation setting Independent

Data bit 8

Parity bit Yes

Even/odd parity Odd

Stop bit 1

Sum check code Yes

Write during RUN Allowed

Setting modifications Allowed/Prohibited

1) Operation setting

• This sets whether to use each of the two Q series C24 interfaces for

independent data communication, or to use the two for linked data

communication.

• The setting and data flow for linked operation is explained in (2).

2) Data bit setting

• This sets the bit length for one character in data communicated with an

external device according to the specifications of the external device.

(When data communication is performed using format 5 of the MC

protocol (for binary code communication), it is necessary to set it to 8

bits when processing the sum check code with the bidirectional

protocol.)

• If 7 bits are set, the data is communicated by ignoring the most

significant bit (8th bit).

3) Parity bit setting

• This sets whether or not a parity bit (vertical parity) is added for one

byte of transmission/receive data, according to the specifications of

the external device.

• The addition of the parity bit to the transmission data and the checking

of the parity bit of receive data are performed by the Q series C24.