www.ti.com

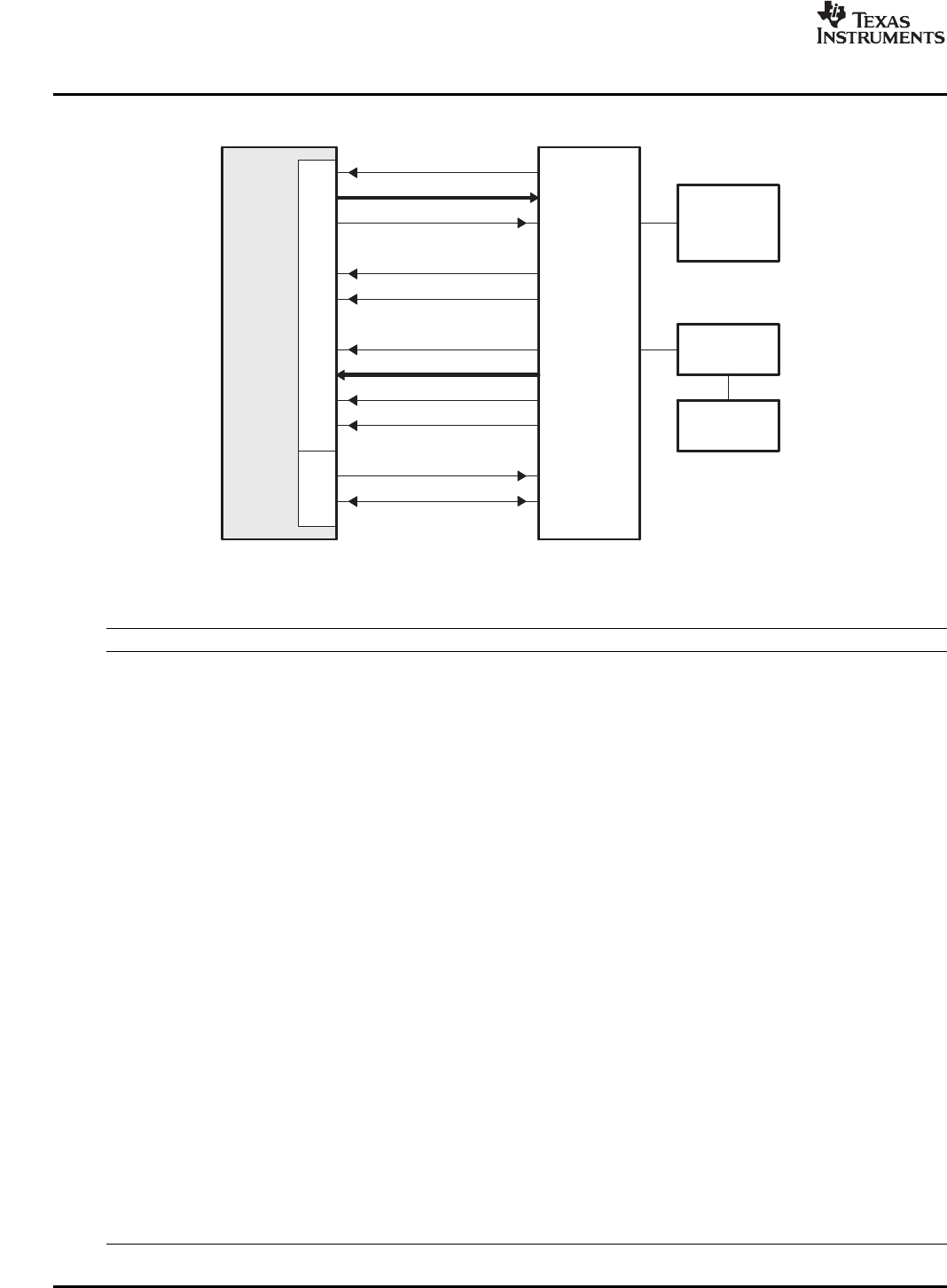

MTCLK

MTXD(3−0)

MTXEN

MCOL

MCRS

MRCLK

MRXD(3−0)

MRXDV

MRXER

MDCLK

MDIO

Physical

layer

device

(PHY)

System

core

Transformer

2.5 MHz

or

25 MHz

RJ−45

EMACMDIO

PeripheralArchitecture

Figure2.TypicalEthernetConfiguration

Table1.EMACandMDIOSignals

SignalTypeDescription

MTCLKITransmitclock(MTCLK).Thetransmitclockisacontinuousclockthatprovidesthetimingreference

fortransmitoperations.TheMTXDandMTXENsignalsaretiedtothisclock.Theclockisgenerated

bythePHYandis2.5MHzat10Mbpsoperationand25MHzat100Mbpsoperation.

MTXD[3-0]OTransmitdata(MTXD).Thetransmitdatapinsareacollectionof4datasignalscomprising4bitsof

data.MTDX0istheleast-significantbit(LSB).ThesignalsaresynchronizedbyMTCLKandvalid

onlywhenMTXENisasserted.

MTXENOTransmitenable(MTXEN).ThetransmitenablesignalindicatesthattheMTXDpinsaregenerating

nibbledataforusebythePHY.ItisdrivensynchronouslytoMTCLK.

MCOLICollisiondetected(MCOL).TheMCOLpinisassertedbythePHYwhenitdetectsacollisiononthe

network.Itremainsassertedwhilethecollisionconditionpersists.Thissignalisnotnecessarily

synchronoustoMTCLKnorMRCLK.Thispinisusedinhalf-duplexoperationonly.

MCRSICarriersense(MCRS).TheMCRSpinisassertedbythePHYwhenthenetworkisnotidleineither

transmitorreceive.Thepinisdeassertedwhenbothtransmitandreceiveareidle.Thissignalisnot

necessarilysynchronoustoMTCLKnorMRCLK.Thispinisusedinhalf-duplexoperationonly.

MRCLKIReceiveclock(MRCLK).Thereceiveclockisacontinuousclockthatprovidesthetimingreference

forreceiveoperations.TheMRXD,MRXDV,andMRXERsignalsaretiedtothisclock.Theclockis

generatedbythePHYandis2.5MHzat10Mbpsoperationand25MHzat100Mbpsoperation.

MRXD[3-0]IReceivedata(MRXD).Thereceivedatapinsareacollectionof4datasignalscomprising4bitsof

data.MRDX0istheleast-significantbit(LSB).ThesignalsaresynchronizedbyMRCLKandvalid

onlywhenMRXDVisasserted.

MRXDVIReceivedatavalid(MRXDV).ThereceivedatavalidsignalindicatesthattheMRXDpinsare

generatingnibbledataforusebytheEMAC.ItisdrivensynchronouslytoMRCLK.

MRXERIReceiveerror(MRXER).ThereceiveerrorsignalisassertedforoneormoreMRCLKperiodsto

indicatethatanerrorwasdetectedinthereceivedframe.Thisismeaningfulonlyduringdata

receptionwhenMRXDVisactive.

MDCLKOManagementdataclock(MDCLK).TheMDIOdataclockissourcedbytheMDIOmoduleonthe

system.ItisusedtosynchronizeMDIOdataaccessoperationsdoneontheMDIOpin.The

frequencyofthisclockiscontrolledbytheCLKDIVbitsintheMDIOcontrolregister(CONTROL).

MDIOI/OManagementdatainputoutput(MDIO).TheMDIOpindrivesPHYmanagementdataintoandoutof

thePHYbywayofanaccessframeconsistingofstartofframe,read/writeindication,PHYaddress,

registeraddress,anddatabitcycles.TheMDIOpinactsasanoutputforallbutthedatabitcycles

atwhichtimeitisaninputforreadoperations.

EthernetMediaAccessController(EMAC)/ 14SPRU941A–April2007

ManagementDataInput/Output(MDIO)

SubmitDocumentationFeedback