www.ti.com

5.30EmulationControlRegister(EMCONTROL)

5.31FIFOControlRegister(FIFOCONTROL)

EthernetMediaAccessController(EMAC)Registers

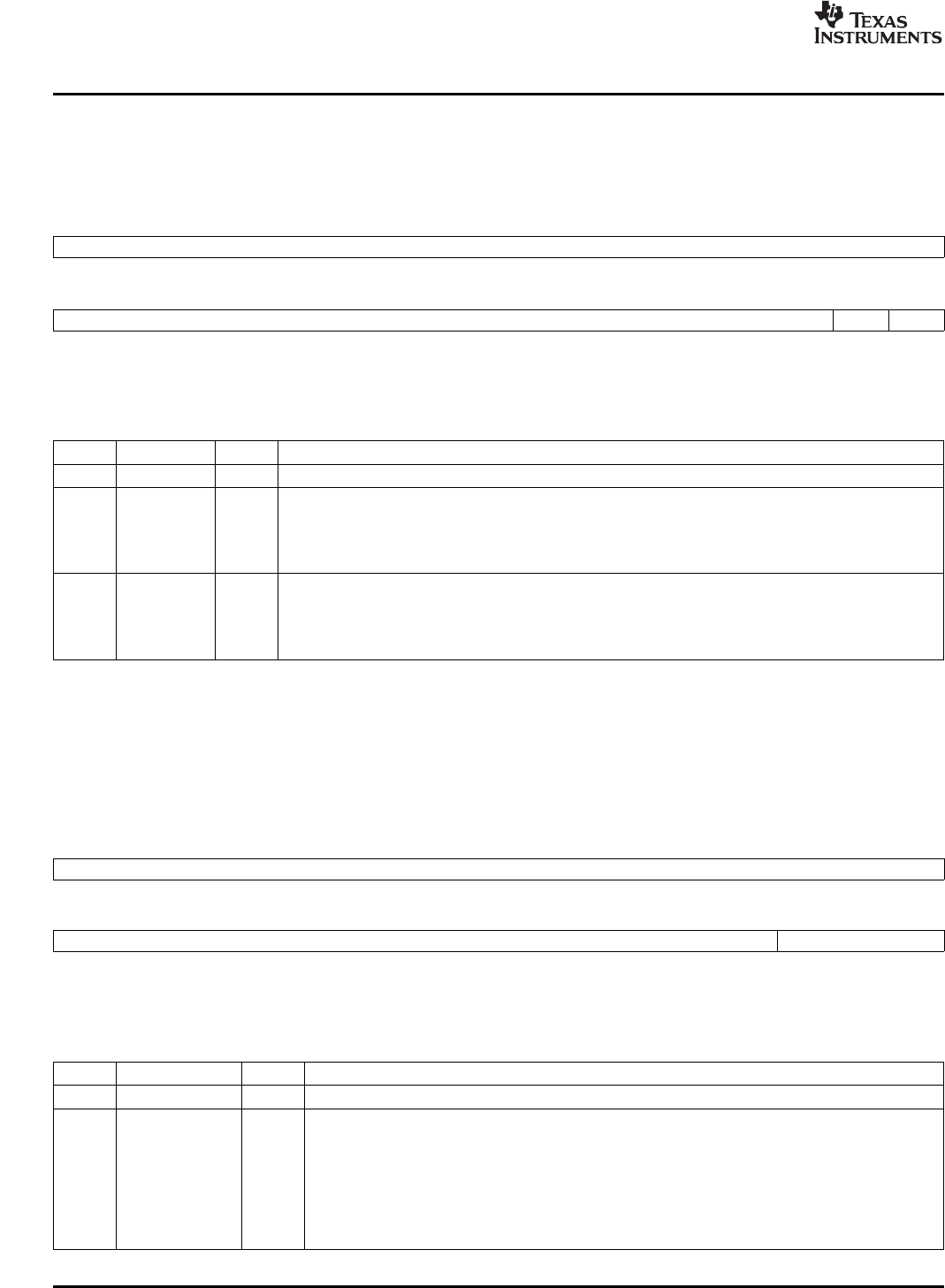

Theemulationcontrolregister(EMCONTROL)isshowninFigure56anddescribedinTable55.

Figure56.EmulationControlRegister(EMCONTROL)

3116

Reserved

R-0

15210

ReservedSOFTFREE

R-0R/W-0R/W-0

LEGEND:R=Readonly;R/W=Read/Write;-n=valueafterreset

Table55.EmulationControlRegister(EMCONTROL)FieldDescriptions

BitFieldValueDescription

31-2Reserved0Reserved

1SOFTEmulationsoftbit.ThisbitisusedinconjunctionwithFREEbittodeterminetheemulationsuspend

mode.ThisbithasnoeffectifFREE=1.

0Softmodeisdisabled.EMACstopsimmediatelyduringemulationhalt.

1Softmodeisenabled.Duringemulationhalt,EMACstopsaftercompletionofcurrentoperation.

0FREEEmulationfreebit.ThisbitisusedinconjunctionwithSOFTbittodeterminetheemulationsuspend

mode.

0Free-runningmodeisdisabled.Duringemulationhalt,SOFTbitdeterminesoperationofEMAC.

1Free-runningmodeisenabled.Duringemulationhalt,EMACcontinuestooperate.

TheFIFOcontrolregister(FIFOCONTROL)isshowninFigure57anddescribedinTable56.

Figure57.FIFOControlRegister(FIFOCONTROL)

3116

Reserved

R-0

15210

ReservedTXCELLTHRESH

R-0R/W-2h

LEGEND:R=Readonly;R/W=Read/Write;-n=valueafterreset

Table56.FIFOControlRegister(FIFOCONTROL)FieldDescriptions

BitFieldValueDescription

31-2Reserved0Reserved

1-0TXCELLTHRESH0-3hTransmitFIFOcellthreshold.Indicatesthenumberof64-bytepacketcellsrequiredtobeinthe

transmitFIFObeforethepackettransferisinitiated.Packetswithfewercellswillbeinitiatedwhen

thecompletepacketiscontainedintheFIFO.Thedefaultvalueis2,but3isalsovalid.0and1are

notvalidvalues.

0-1hNotavalidvalue.

2hTwo64-bytepacketcellsrequiredtobeinthetransmitFIFO.

3hThree64-bytepacketcellsrequiredtobeinthetransmitFIFO.

98EthernetMediaAccessController(EMAC)/SPRU941A–April2007

ManagementDataInput/Output(MDIO)

SubmitDocumentationFeedback