www.ti.com

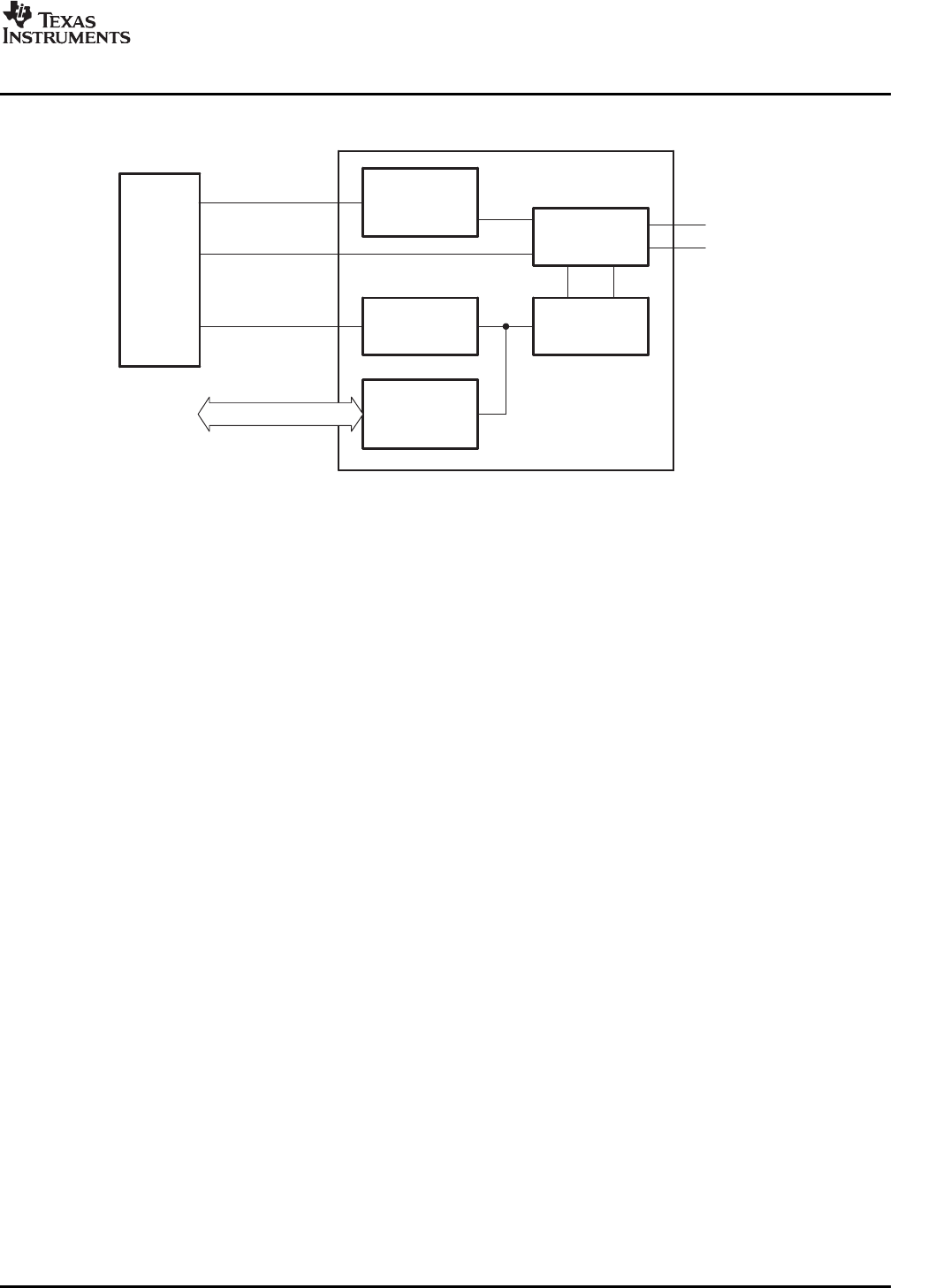

EMAC

control

module

Control

registers

and logic

PHY

monitoring

Peripheral

clock

MDIO

clock

generator

USERINT

MDIO

interface

polling

PHY

MDCLK

MDIO

LINKINT

Configuration bus

2.7.1.1MDIOClockGenerator

2.7.1.2GlobalPHYDetectionandLinkStateMonitoring

2.7.1.3ActivePHYMonitoring

2.7.1.4PHYRegisterUserAccess

PeripheralArchitecture

Figure9.MDIOModuleBlockDiagram

TheMDIOclockgeneratorcontrolstheMDIOclockbasedonadivide-downoftheperipheralclock

(PLL1/6)intheEMACcontrolmodule.TheMDIOclockisspecifiedtorunupto2.5MHZ,althoughtypical

operationwouldbe1.0MHZ.Sincetheperipheralclockfrequencyisvariable(PLL1/6),theapplication

softwareordrivercontrolsthedivide-downamount.

TheMDIOmodulecontinuouslypollsall32MDIOaddressesinordertoenumeratethePHYdevicesinthe

system.ThemoduletrackswhetherornotaPHYonaparticularaddresshasresponded,andwhetheror

notthePHYcurrentlyhasalink.Usingthisinformationallowsthesoftwareapplicationtoquickly

determinewhichMDIOaddressthePHYisusing.

OnceaPHYcandidatehasbeenselectedforuse,theMDIOmoduletransparentlymonitorsitslinkstate

byreadingtheMDIOPHYlinkstatusregister(LINK).LinkchangeeventsarestoredontheMDIOdevice

andcanoptionallyinterrupttheCPU.ThisallowsthesystemtopollthelinkstatusofthePHYdevice

withoutcontinuouslyperformingcostlyMDIOaccesses.

WhentheCPUmustaccessMDIOforconfigurationandnegotiation,thePHYaccessmoduleperforms

theactualMDIOreadorwriteoperationindependentoftheCPU.ThisallowstheCPUtopollfor

completionorreceiveaninterruptwhenthereadorwriteoperationhasbeenperformed.Theuseraccess

registersUSERACCESSnallowsthesoftwaretosubmittheaccessrequestsforthePHYconnectedtothe

device.

SPRU941A–April2007EthernetMediaAccessController(EMAC)/29

ManagementDataInput/Output(MDIO)

SubmitDocumentationFeedback