www.ti.com

5.15ReceiveInterruptMaskClearRegister(RXINTMASKCLEAR)

EthernetMediaAccessController(EMAC)Registers

Thereceiveinterruptmaskclearregister(RXINTMASKCLEAR)isshowninFigure41anddescribedin

Table40.

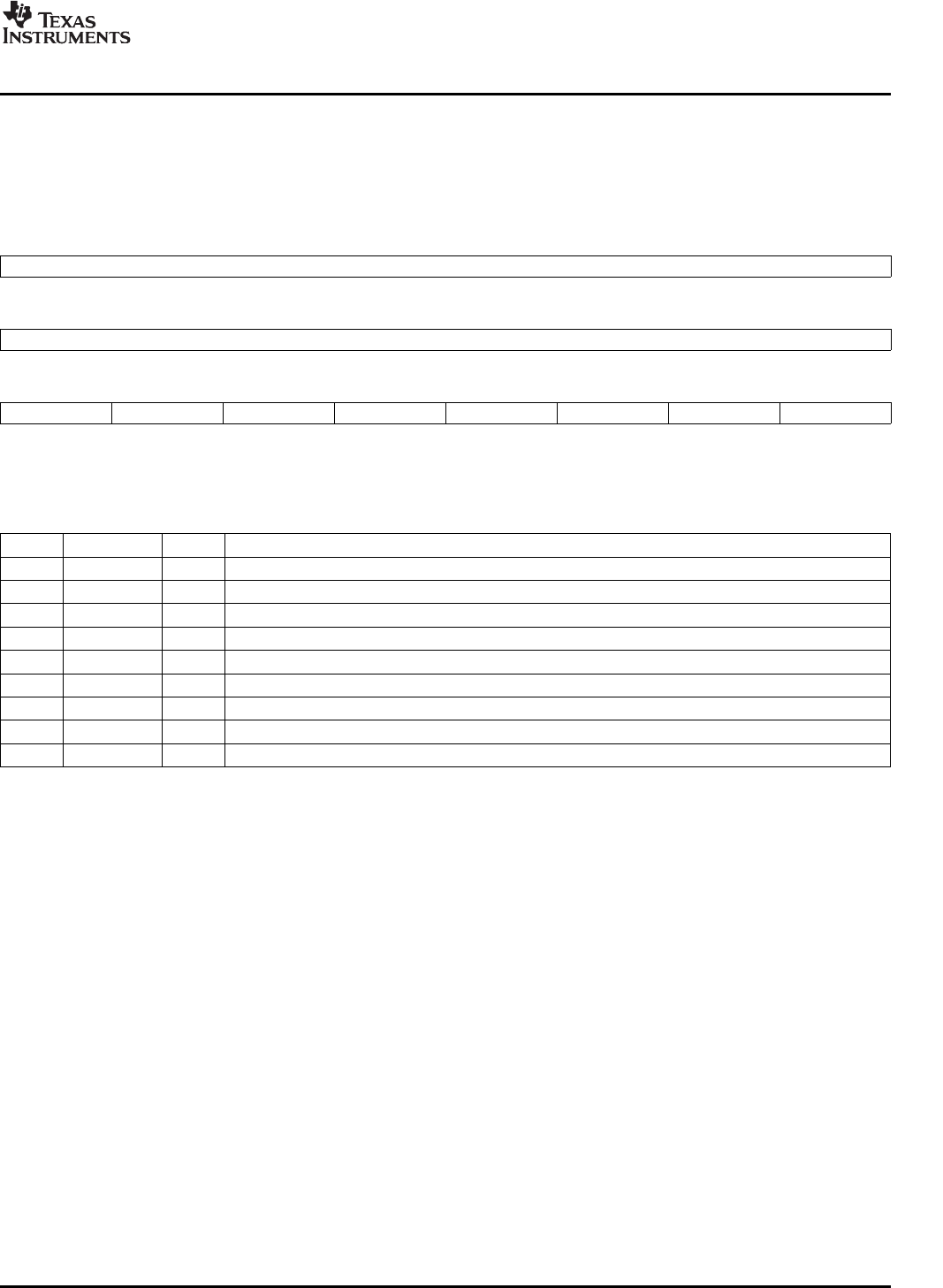

Figure41.ReceiveInterruptMaskClearRegister(RXINTMASKCLEAR)

3116

Reserved

R-0

158

Reserved

R-0

76543210

RX7MASKRX6MASKRX5MASKRX4MASKRX3MASKRX2MASKRX1MASKRX0MASK

R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0

LEGEND:R=Readonly;R/W=Read/Write;WC=Write1toclear,writeof0hasnoeffect;-n=valueafterreset

Table40.ReceiveInterruptMaskClearRegister(RXINTMASKCLEAR)FieldDescriptions

BitFieldValueDescription

31-8Reserved0Reserved

7RX7MASK0-1Receivechannel7maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

6RX6MASK0-1Receivechannel6maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

5RX5MASK0-1Receivechannel5maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

4RX4MASK0-1Receivechannel4maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

3RX3MASK0-1Receivechannel3maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

2RX2MASK0-1Receivechannel2maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

1RX1MASK0-1Receivechannel1maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

0RX0MASK0-1Receivechannel0maskclearbit.Write1todisableinterrupt,awriteof0hasnoeffect.

SPRU941A–April2007EthernetMediaAccessController(EMAC)/83

ManagementDataInput/Output(MDIO)

SubmitDocumentationFeedback