www.ti.com

2.8EMACModule

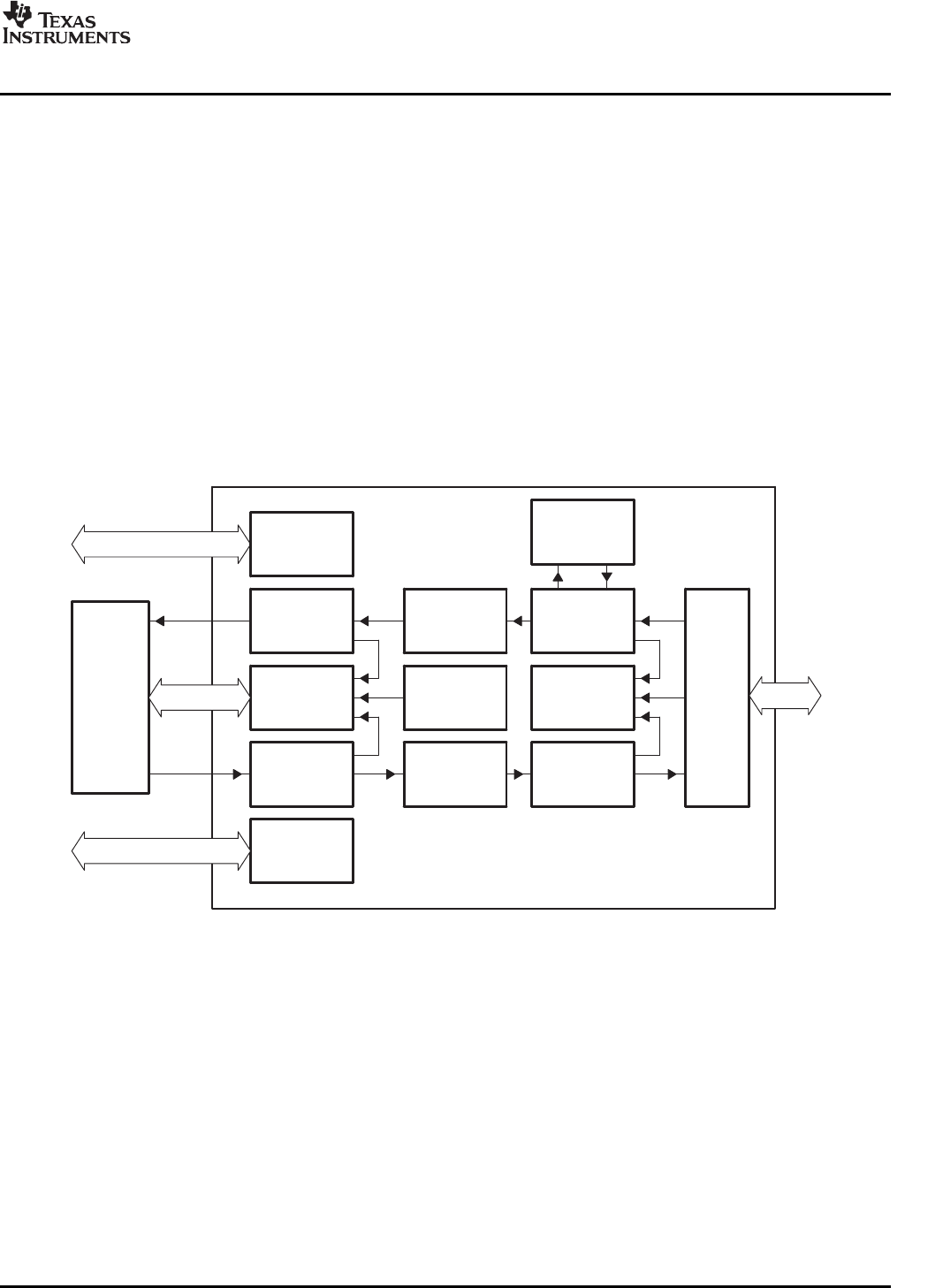

2.8.1EMACModuleComponents

Clock and

reset logic

Receive

DMA engine

Interrupt

controller

Transmit

DMA engine

Control

registers

Configuration bus

EMAC

control

module

Configuration bus

RAM

State

FIFO

Receive

FIFO

Transmit MAC

transmitter

Statistics

receiver

MAC

SYNC

MII

address

Receive

2.8.1.1ReceiveDMAEngine

2.8.1.2ReceiveFIFO

2.8.1.3MACReceiver

PeripheralArchitecture

ThissectiondiscussesthearchitectureandbasicfunctionoftheEMACmodule.

TheEMACmodule(Figure10)interfacestotheoutsideworldthroughtheMediaIndependentInterface

(MII)andinterfacestothesystemcorethroughtheEMACcontrolmodule.TheEMACconsistsofthe

followinglogicalcomponents:

•Thereceivepathincludes:receiveDMAengine,receiveFIFO,andMACreceiver

•Thetransmitpathincludes:transmitDMAengine,transmitFIFO,andMACtransmitter

•Statisticslogic

•StateRAM

•Interruptcontroller

•Controlregistersandlogic

•Clockandresetlogic

Figure10.EMACModuleBlockDiagram

ThereceiveDMAengineistheinterfacebetweenthereceiveFIFOandthesystemcore.Itinterfacesto

theCPUthroughthebusarbiterintheEMACcontrolmodule.ThisDMAengineistotallyindependentof

thedeviceDMA.

ThereceiveFIFOconsistsofthreecellsof64-byteseachandassociatedcontrollogic.TheFIFObuffers

receivedatainpreparationforwritingintopacketbuffersindevicememory.

TheMACreceiverdetectsandprocessesincomingnetworkframes,de-framesthem,andputstheminto

thereceiveFIFO.TheMACreceiveralsodetectserrorsandpassesstatisticstothestatisticsRAM.

SPRU941A–April2007EthernetMediaAccessController(EMAC)/33

ManagementDataInput/Output(MDIO)

SubmitDocumentationFeedback