Intel® Server Board Set SE8500HW4 I/O Subsystems

Revision 1.0

Intel order number D22893-001

11

3. I/O Subsystems

3.1 PCI Subsystem

The PCI subsystem consists of eight slots, seven available to standard PCI adapters and one

for the Intel

®

Server Board Set SE8500HW4-specific Intel

®

Fibre Channel Module.

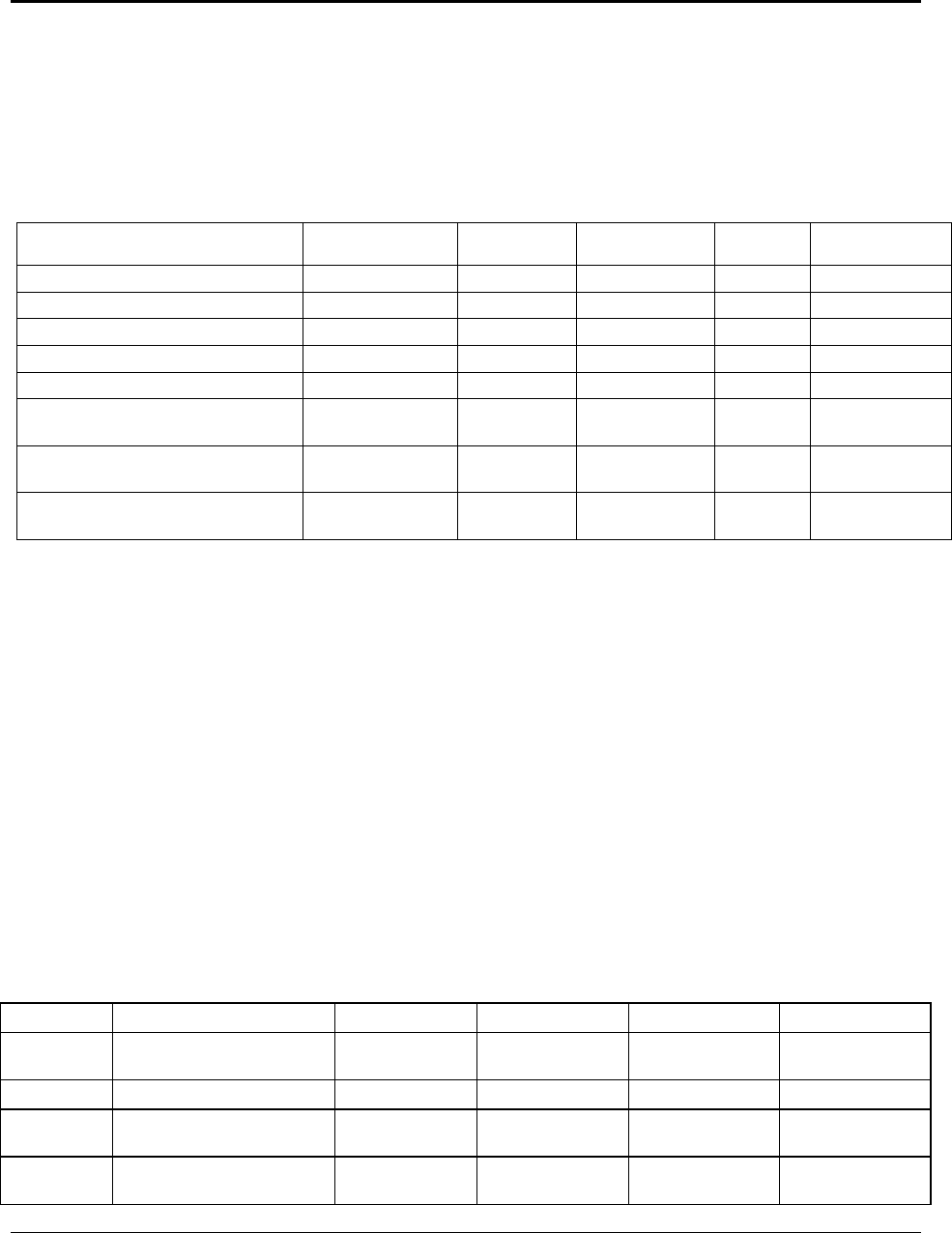

Table 3. PCI Expansion Slot Features

Segment Slot Hot Plug Technology Width Bandwidth

(GB/s)

North Bridge (C) 1 Yes PCI Express* x8 4

PXH (A) 2 Yes PCI-X* 133 64-bit 1

North Bridge (D) 3 Yes PCI Express x4 2

North Bridge (B) 4 Yes PCI Express x4 2

North Bridge (B) 5 Yes PCI Express x4 2

Intel

®

IOP332 Storage I/O

Processor (B)

6 No PCI-X 100 64-bit 0.8

Intel IOP332 Storage I/O

Processor (B)

7 No PCI-X 100 64-bit 0.8

Intel IOP332 Storage I/O

Processor (A)

Fibre Channel No PCI-X 100 64-bit 0.8

3.1.1 PCI Interrupts

PCI Express interrupts are delivered in-band over the PCI Express bus via the Message Signal

Interrupt (MSI) mechanism.

PCI and PCI-X devices can deliver interrupts either by asserting IRQ signals that are routed to

the PXH or Intel

®

IOP332 Storage I/O Processor IOxAPIC, or over the PCI-X bus via MSI. In

either case, the PXH and/or Intel® IOP332 Storage I/O Processor forward the interrupt to the

NB as an Inbound Write for the processor to handle the event.

Table 4 describes how the interrupts for each of the PCI devices are mapped to the PXH and

Intel

®

IOP332 Storage I/O Processor.

Table 4. PCI Interrupt Mapping

Device APIC INTA# INTB# INTC# INTD#

Broadcom*

BCM5704

PXH (B) PX2B_IRQ0_N PX2B_IRQ1_N

Slot 2 PXH (A) PX2A_IRQ0_N PX2A_IRQ1_N PX2A_IRQ2_N PX2A_IRQ3_N

Slot 6 Intel

®

IOP332 Storage I/O

Processor (B)

PX1B_XINT4_N PX1B_XINT5_N PX1B_XINT6_N PX1B_XINT7_N

Slot 7 Intel IOP332 Storage I/O

Processor (B)

PX1B_XINT6_N PX1B_XINT7_N PX1B_XINT4_N PX1B_XINT5_N