Intel® Server Board Set SE8500HW4 Server Management

Revision 1.0

Intel order number D22893-001

35

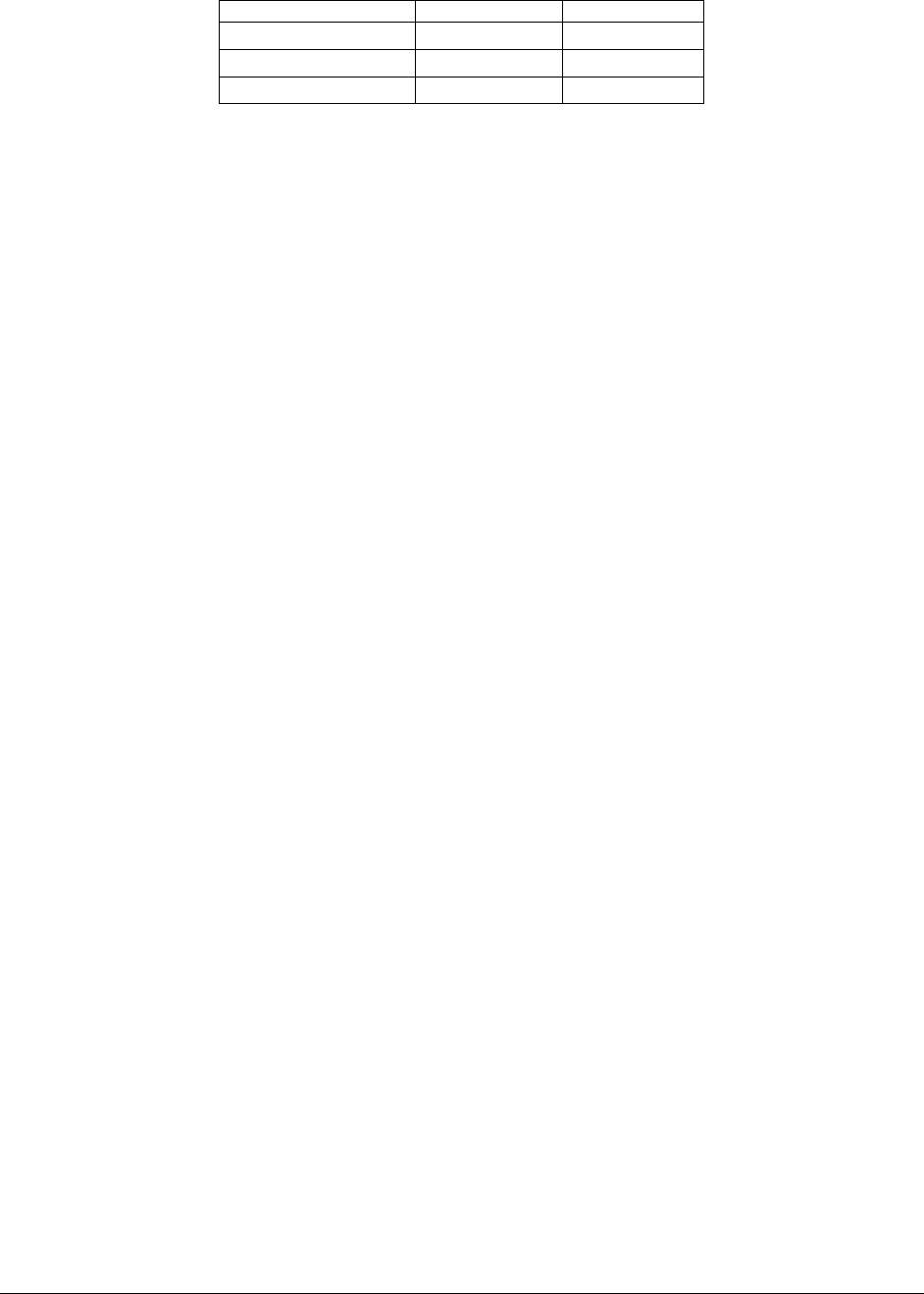

ACPI Sleep State Power Switch Reset Switch

S0 Protected Protected

S1 Partial

1

Protected

S5 Unprotected Unprotected

1. The system will wake from the power switch but holding the button for four seconds is

blocked.

5.4 Fault Resilient Booting (FRB)

When a system reset signal is recognized by the chipset, all processors execute initialization

microcode and one is chosen as the bootstrap processor (BSP). The BSP executes the Power

On Self Test (POST) for the BIOS and remains the only processor executing commands until

control is handed over to an operating system.

Fault Resilient Booting (FRB) is a set of BIOS/BMC algorithms and hardware support that allow,

in certain conditions, a multiprocessor system to boot even in the event of a failure with the

bootstrap processor (BSP). The FRB algorithms detect a BSP failure, then disable that

processor and reset the system so another processor will be selected as the BSP. For FRB3,

the BMC relies on the BIOS to assert the FRB3 timer halt signal, which indicates to the BMC

that the BSP is successfully running code.

5.4.1 FRB3

The BMC starts a five second timer when the system is powered on or hard reset. The BIOS

requests the BMC to stop this timer during POST. If the BIOS were able to stop this timer, the

BMC assumes that the BSP processor had no errors. If is not stopped and expires, the BMC will

reset the system. If the timer expires on the second boot, the BMC disables the current BSP,

logs the event, selects another BSP, and resets the system.

This process repeats until either the system boots without an FRB3 timeout, or all of the

processors have been disabled. The BMC will enter a desperation mode if all the processors

have been disabled. In this mode the BMC will ignore the processor error history and attempt to

boot the system one processor at a time. If all the processors have failed in desperation mode,

the BMC will enter final desperation mode, where the FRB3 algorithm is disabled and the first

processor is allowed to boot into POST. In this mode, a beep code will be generated to notify

the user the system has reached an FRB3 failure.

FRB3 requires multiple processors. The BMC verifies that there are at least two processors

installed in the system. If only one processor is present the FRB3 timer will not be started. The

Intel

®

Server Board Set SE8500HW4 Mainboard also includes a jumper to disable the FRB3

timer.