Intel® Server Board Set SE8500HW4 Memory Board Intel® Server Board Set SE8500HW4

Revision 1.0

Intel order number D22893-001

22

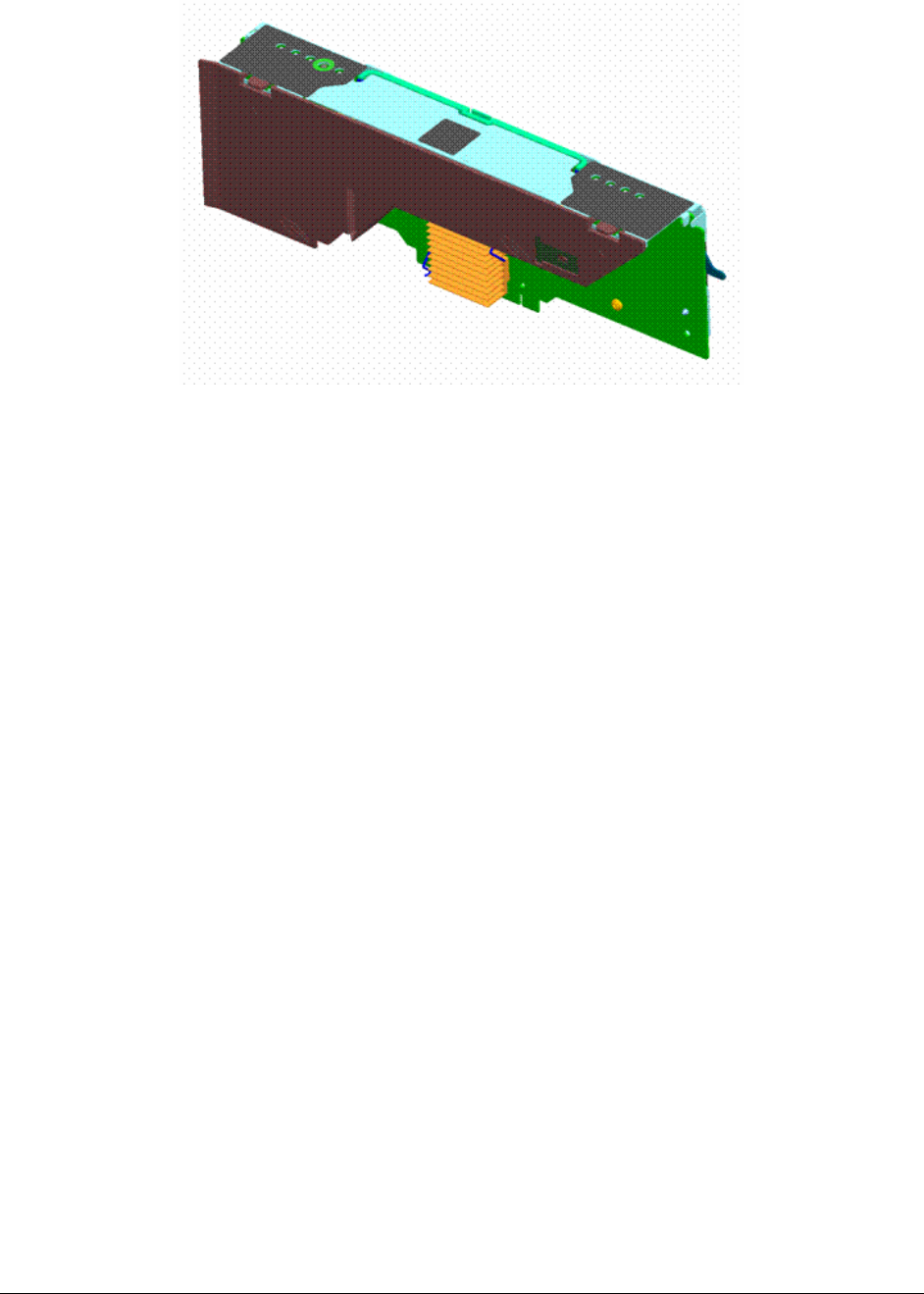

Figure 5. Memory Board Component Diagram

4.1 DDR2 DIMM Support

DDR2 memory offers an effective doubling of the clock rate over DDR memory since data

transfers happen on both the rising and falling edge of the clock (double pumped). Due to the

lower clock frequency, and improved manufacturing technology, a significant power savings can

be achieved, especially when the data bus is not active.

The Intel

®

Server Board Set SE8500HW4 Memory Board supports DDR2 400MHz (also referred

to as PC2-3200) registered ECC SDRAM with On Die Termination (ODT). Both single-rank and

dual-rank technologies are supported, however unbuffered and non-ECC will not function in the

Intel

®

Server Board Set SE8500HW4. Within a single bank, both DIMMs must be identical. (The

DIMMs must be identical in size and in the number of devices on the DIMM.)

Speeds less than DDR2 400MHz may be used, but performance will be reduced. Intel has only

validated DDR2 400MHz SDRAM for specific memory parts; refer to the Intel

®

Server Board Set

SE8500HW4 Board Memory Qualification List

4.2 Installation Order

When only using two memory DIMMs, the first pair of sockets, DIMM_1A and DIMM_1B, must

be populated. When using a mixture of single-rank and dual-rank memory DIMMs on one

Memory Board, the dual-rank DIMMs must be installed in the first pair of sockets.

4.3 Memory Initialization

The XMB provides hardware memory initialization. The initialization engine performs two

passes. On the first pass, it writes the entire segment. On the second pass, it reads and tests

the entire segment. Any errors are logged with the failing DIMM being flagged for BIOS.