Server Management Intel® Server Board Set SE8500HW4

Revision 1.0

Intel order number D22893-001

36

5.4.2 FRB2

The BIOS requests the BMC to start a second 10-minute timer to ensure the system completes

the BIOS POST. The FRB2 timer is enabled before the FRB3 timer is disabled to prevent a gap

in FRB coverage. The BIOS requests the BMC to disable the FRB2 timer before the option

ROMs are scanned, the BIOS setup is entered, or prior to displaying a request for a boot

password.

If the FRB2 timer expires and the BIOS is configured with reset as the action to take on the

timeout, the BMC will log an FRB2 timeout event with the last POST code generated and reset

the system. By default the BSP processor will not be disabled on an FRB2 timeout. There is a

BIOS option to disable the processor in an FRB2 timeout, but since this timeout may not be a

processor failure, the default behavior is to only reset the system. If during the next boot the

BIOS can determine that the last boot failure was processor related, the BIOS requests the

BMC to disable the BSP and reset the system.

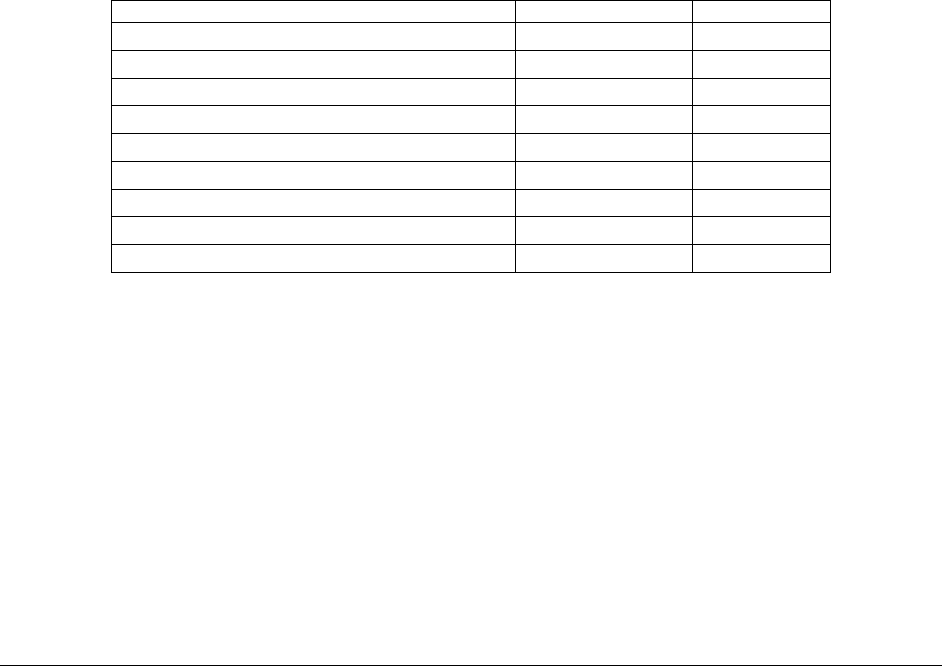

5.5 Reset Control

Reset circuitry on the Mainboard is aware of resets from several sources and determines the

proper reset sequence for the different types of resets. Table 13 defines all the reset sources

and the actions taken by the system.

Table 13. System Reset Sources and Actions

Reset Source System Reset? BMC Reset?

Standby power comes up No (no DC power) Yes

Main system power comes up Yes No

Reset button pushed Yes No

Warm reset Yes No

Set processor state or chasis control command Yes No

Watchdog timer configured for reset Yes No

FRB3 timeout Yes No

PEF action Optional No

Exit BMC firmware update mode No Yes

5.5.1 Front Panel Reset

The reset button is a momentary contact button on the front panel. It is routed through the front

panel connector to the BMC, which monitors and de-bounces the signal.

If secure mode is enabled, or the button is forced protected, the reset button does not reset the

system, and a platform security violation attempt event message is logged. The reset button is

also disabled in sleep mode.

5.5.2 Warm Reset

A warm reset does not remove power from the system and is usually triggered by software or

from the ICH5 (e.g. when Ctrl-Alt-Del is pressed). This reset can also result if the BMC detects