Intel® Server Board Set SE8500HW4 I/O Subsystems

Revision 1.0

Intel order number D22893-001

13

3.1.3 Bus Arbitration Signals

Request (REQ#) signals indicate to the bus arbiter that an agent/device desires use of the bus.

The Grant (GNT#) signal indicates to the agent/device that access to the bus has been granted.

Every master has its own REQ#, which must be tri-stated while RST# is asserted. These are

point-to-point signals which are assigned to every bus master.

In the Intel

®

Server Board Set SE8500HW4 there is one arbiter for each PCI bus on the PXH

and Intel

®

IOP332 Storage I/O Processor. The PXH contains an arbiter for slot 2 and the

BCM5704 and the Intel

®

IOP332 Storage I/O Processor contains an arbiter for slots 6 and 7, LSI

Logic 53C1030, and the Intel

®

Fibre Channel Module.

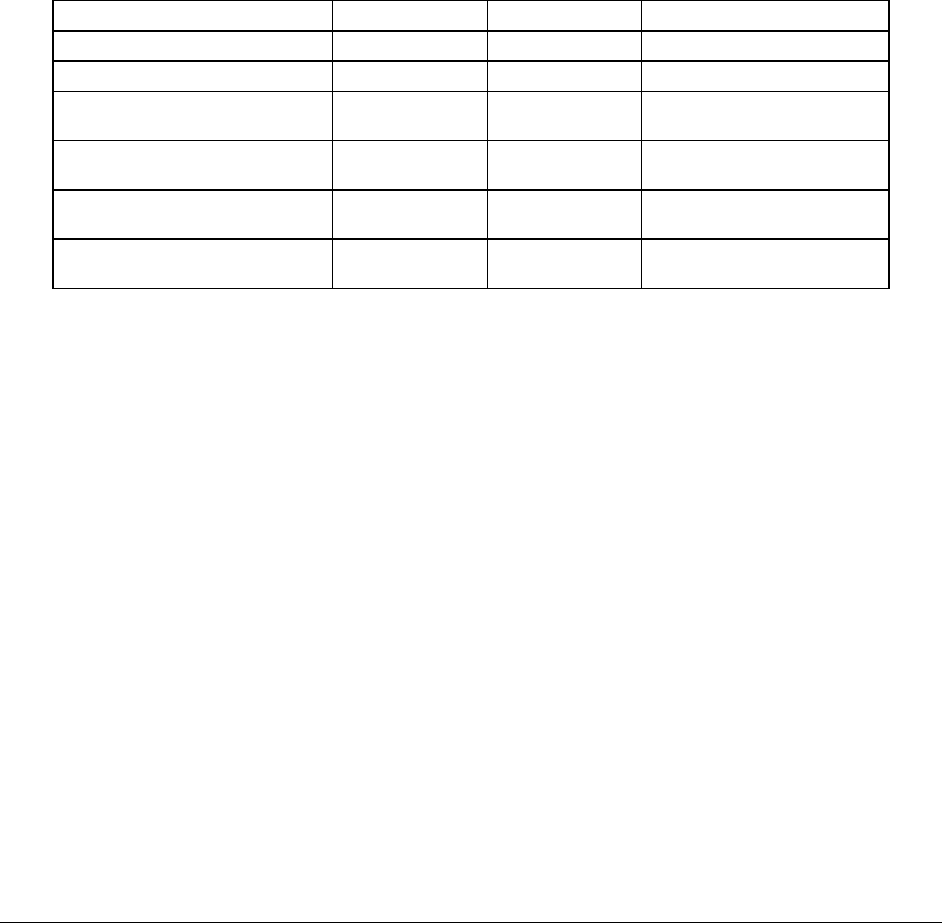

Table 6. Arbitration Connections

Device REQ# GNT# Host Bridge

Broadcom* BCM5704 PX2B_REQ0_N PX2B_GNT0_N PXH (B)

Slot 2 PX2A_REQ0_N PX2A_GNT0_N PXH (A)

Slot 6 PX1B_REQ1_N PX1B_GNT1_N Intel

®

IOP332 Storage I/O

Processor (B)

Slot 7 PX1B_REQ0_N PX1B_GNT0_N Intel IOP332 Storage I/O

Processor (B)

LSI Logic* 53C1030 PX1A_REQ0_N PX1A_GNT0_N Intel IOP332 Storage I/O

Processor (A)

Intel

®

Fibre Channel Module PX1A_REQ1_N PX1A_GNT1_N Intel IOP332 Storage I/O

Processor (A)

3.1.4 Wake On LAN

Wake On LAN (WOL) is supported on the Intel

®

Server Board Set SE8500HW4 either from PCI

devices through the PME# signal, or PCI Express via the WAKE# signal.

Any PCI Express adapter can generate a wake event by asserting the WAKE# signal. This

signal is OR’d to all other PCI Express WAKE# signals and routed to the ICH5 after being

qualified with intrusion and a prior graceful shutdown. The assertion of a WAKE# signal will

cause the system to return to the ACPI S0 sleep state. Once system power is up and the PCI

Express devices are configured, a PME message is sent to the NB identifying the device that

woke the system.

For all the PCI devices or the Ethernet controller, PME# is handled similarly to the PCI Express

WAKE# signal. All PME# signals are OR’d together and routed to the ICH5 after being qualified

with intrusion and a prior graceful shutdown. The PME assertion wakes the system but does not

generate an interrupt from the ICH5. Once the system is powered up, the PXH or Intel

®

IOP332

Storage I/O Processor generate a PME interrupt message to the operating system. The

operating system determines which slot is the PME source by polling the PXH and Intel

®

IOP332 Storage I/O Processor.